8 Minuten

Apple und Qualcomm haben laut jüngsten Stellenanzeigen stillschweigend Interesse an Intels fortschrittlicher Packaging-Technologie signalisiert. Während Chip-Designer nach Wegen suchen, Leistung und Integration zu steigern, rücken Intels EMIB- und Foveros-Lösungen zunehmend in den Fokus — und dieses Interesse könnte die Wettbewerbslandschaft für Advanced Packaging und Foundry-Dienstleistungen nachhaltig verändern. Die Diskussion um heterogene Integration, Chiplets und 3D-Stacking gewinnt an Bedeutung, da Systemarchitekten alternative Wege suchen, um die Grenzen der traditionellen Fertigung und der Mooreschen Gesetzmäßigkeiten zu überwinden.

Warum die großen Tech-Firmen über Mooresches Gesetz hinausblicken

Das Mooresche Gesetz liefert nicht mehr die einfachen Leistungs- und Kapazitätsgewinne, die es früher gebracht hat. Transistor-Skalierung allein reicht nicht mehr aus, um die steigenden Anforderungen an Bandbreite, Energieeffizienz und Leistung moderner Systeme zu erfüllen. Deshalb verlässt sich die Branche verstärkt auf fortschrittliche Verpackungstechniken (Advanced Packaging), um Chips innerhalb eines einzigen Gehäuses zu stapeln, zu verbinden und zu skalieren. Diese Packaging-Technologien ermöglichen es, mehrere spezialisierte Chiplets oder gestapelte Dies zu kombinieren und so heterogene Systeme zu realisieren, die Logik, Speicher und I/O dichter und effizienter integrieren.

Solche Ansätze sind besonders relevant für Hochleistungsrechner, Beschleuniger (GPUs), Netzwerk-Applikationen und proprietäre System-on-Chip-Designs. Firmen wie Nvidia und AMD sowie die Custom-Silicon-Teams großer Endkunden wie Apple und Qualcomm setzen zunehmend auf Integration auf Systemebene: Chiplets, HBM als externes oder integratives Speicher-Subsystem sowie spezialisierte I/O-Module für hohe Bandbreite. Parallel dazu verursachen wachsende Nachfrage und knappe Kapazitäten bei etablierten Foundries Engpässe, die Designteams zwingen, alternative Packaging-Ökosysteme in Betracht zu ziehen.

Die Dominanz von TSMC in der Kategorie Advanced Packaging, insbesondere mit Lösungen wie CoWoS (Chip on Wafer on Substrate), hat jahrelang eine klare Supply-Chain-Struktur geschaffen. Doch steigende Auftragsvolumina für GPU- und CPU-Kunden sowie Priorisierungen bei der Auftragsvergabe führen zu Kapazitätsengpässen. Diese Engpässe schaffen Chancen für alternative Anbieter und Technologien, die kompatible oder komplementäre Integrationspfade anbieten — ein Marktumfeld, in dem Intel mit seinen Packaging-Technologien und seinem fertigungstechnischen Ökosystem versucht, Marktanteile zu gewinnen.

EMIB und Foveros: zwei unterschiedliche Wege zu dichteren Chips

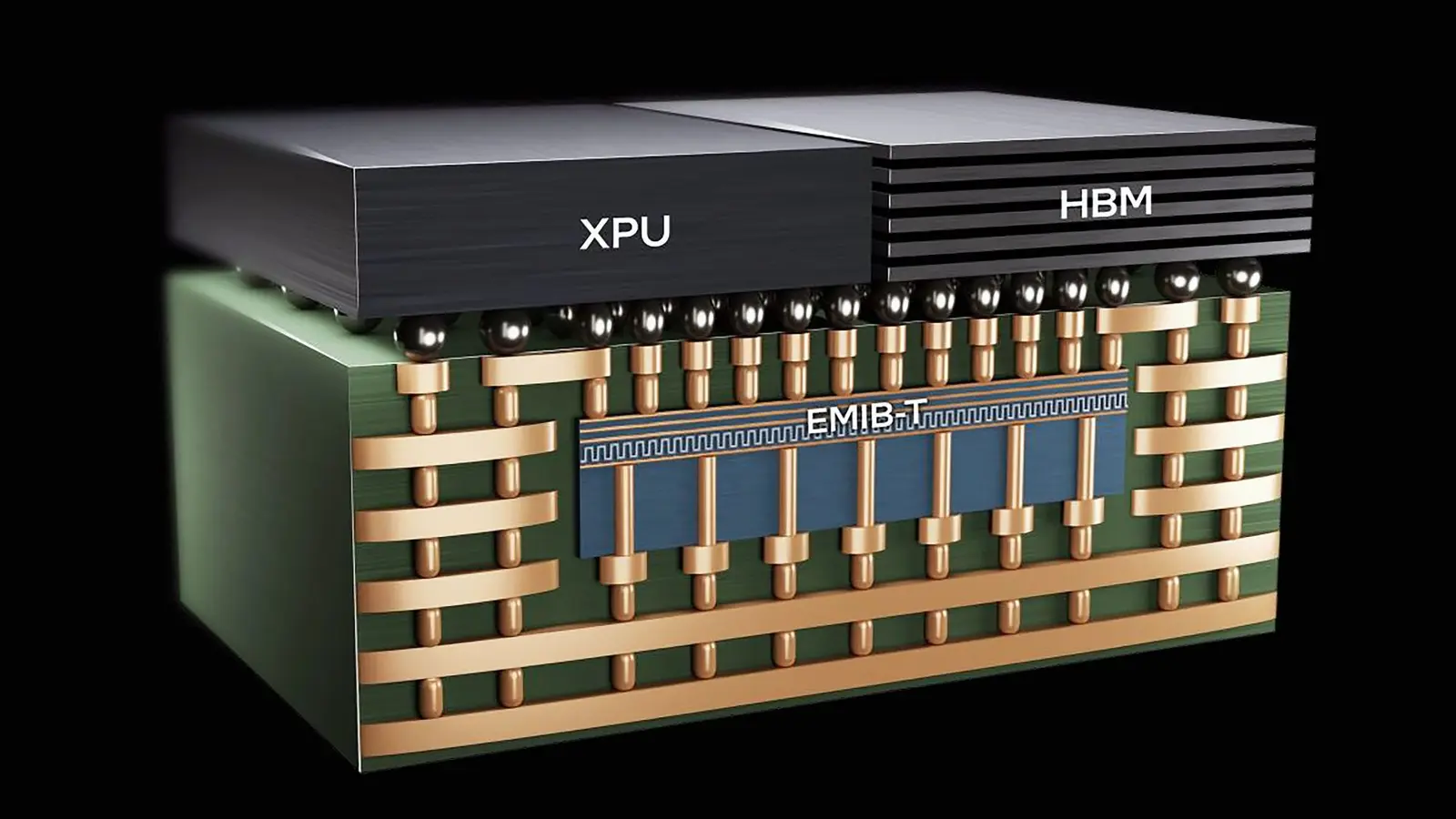

Intels EMIB (Embedded Multi-Die Interconnect Bridge) nutzt kleine Siliziumbrücken, um mehrere Chiplets innerhalb eines Pakets zu verbinden, ohne einen großen Interposer zu benötigen. Durch diesen lokalisierten Verbindungsansatz lassen sich hohe Bandbreiten zwischen benachbarten Dies erreichen, während Materialkosten und Fertigungsaufwand gegenüber ganzen Interposer-Lösungen reduziert werden. EMIB bietet dadurch eine Balance aus Leistung, Kosten und Designflexibilität, vor allem für Systeme, bei denen bestimmte Dies mit hoher Bandbreite gekoppelt werden müssen, beispielsweise eine CPU oder ein I/O-Die mit HBM-Controllern.

Im Kontrast dazu verfolgt Foveros einen vertikalen Integrationsansatz: Das Die-Stacking. Mithilfe von Through-Silicon Vias (TSVs) und einer feinpitchigen vertikalen Verbindungsstruktur ermöglicht Foveros das Stapeln von Logik- und Speicher-Dies übereinander. Diese 3D-Integration reduziert die physische Distanz zwischen Komponenten, senkt Latenzen und kann die Energieeffizienz verbessern, da Signalwege kürzer sind und die Infrastruktur für Datentransfer dichter gepackt wird. Foveros eignet sich besonders für Designs, bei denen enge Kopplung zwischen Rechenlogik und Speicher entscheidend ist, etwa bei speziellen Beschleunigern oder energieeffizienten mobilen Prozessoren.

Beide Methoden — EMIB für laterale Verbindungen und Foveros für vertikales Stacking — adressieren unterschiedliche architektonische Anforderungen. Während EMIB eine kosteneffiziente Möglichkeit bietet, heterogene Chiplets nebeneinander zu integrieren, eröffnet Foveros Optionen für extrem dichte, latenzkritische Verbindungen über mehrere Die-Ebenen hinweg. Für Designer, die Vorteile heterogener Integration suchen, ist die Möglichkeit, zwischen oder sogar einer Kombination dieser Technologien zu wählen, strategisch wertvoll: sie verringert die Abhängigkeit von der Packaging-Roadmap eines einzelnen Foundrys und erhöht die Flexibilität bei Leistungs-, Kosten- und Lieferkettenentscheidungen.

Aus technischer Sicht sind beide Ansätze nicht frei von Kompromissen: EMIB erfordert präzise Planungen der Platzierung und thermischen Verteilung, während Foveros Fertigungs- und Testherausforderungen mit sehr feinem Pitch und thermischem Management mitbringt. Dennoch bieten sie attraktive Pfade für die Optimierung von Systemleistung, Integrationstiefe und Time-to-Market für kundenindividuelle Siliziumprojekte (custom silicon).

Hinweise aus Stellenanzeigen: Apple- und Qualcomm-Ausschreibungen

Vor Kurzem aufgetauchte Stellenanzeigen von Apple und Qualcomm listen Erfahrungen mit Intels EMIB und anderen Packaging-Technologien als Anforderung oder Vorteil auf. Apples Ausschreibung für einen DRAM-Verpackungsingenieur erwähnt explizit Technologien wie CoWoS, EMIB, SoIC und PoP. Bei Qualcomm nennt eine Stellenausschreibung für einen Director of Product Management im Data-Center-Bereich ebenfalls Vertrautheit mit EMIB als wünschenswertes Profil. Solche Anforderungen deuten darauf hin, dass die jeweiligen Engineering-Teams aktiv Technologien evaluieren, Integrationsszenarien planen und möglicherweise Proof-of-Concepts entwickeln.

Stellenanzeigen sind zwar keine direkten Belege für abgeschlossene Lieferverträge, doch sie gelten in der Industrie als frühe Indikatoren für technologische Evaluierungen und interne Roadmap-Anpassungen. Wenn zwei große Akteure unabhängig voneinander dieselben Packaging-Technologien erwähnen, deutet das auf eine ernsthafte Prüfung hin — sei es zur Diversifizierung von Lieferketten, zur Sicherstellung von Kapazitäten oder zur Vorbereitung auf mögliche Fertigungsalternativen.

Recruiting-Anforderungen spiegeln häufig längerfristige strategische Überlegungen wider: Firmen bauen Kompetenzen auf, um später flexibel Technologieentscheidungen treffen zu können. Insbesondere bei proprietären SoC-Programmen (Custom Silicon) sind frühe Rekrutierungen, interne Evaluierungen und Labortests normale Schritte, bevor formelle Partnerschaften oder Volumenaufträge vergeben werden. Daher können solche Job-Listings als ein Hinweis gelesen werden, dass Apple und Qualcomm ihre Packaging-Optionen prüfen — inklusive einer möglichen Nutzung von Intels EMIB- oder Foveros-Ökosystem.

Was das für den Foundry-Markt bedeuten könnte

Entscheiden sich Apple, Qualcomm oder andere große Designer tatsächlich für Intel als Partner im Bereich Advanced Packaging, wären die Auswirkungen erheblich. Erstens würde dies bestätigen, dass Intels Ökosystem und Infrastruktur ausreichend ausgereift sind, um anspruchsvolle, führende Designprogramme zu unterstützen. Eine solche Bestätigung könnte zusätzliche Kunden anziehen, die nach Alternativen zu etablierten Foundries suchen.

Zweitens würde eine stärkere Nutzung von Intels Packaging-Kapazitäten den Druck auf TSMC und andere Anbieter verringern, deren fortschrittliche Packaging-Linien derzeit durch hohe GPU- und CPU-Volumina ausgelastet sind. Mehr Wettbewerb und zusätzliche Kapazitäten geben Designteams mehr Verhandlungsspielraum, reduzieren Auslieferungsengpässe und verbessern die Planbarkeit für Produkt-Roadmaps. Langfristig könnte das die Pricing-Dynamik verändern und zu diversifizierteren Supply-Chain-Strategien führen.

Nvidia-CEO Jensen Huang hat in der Vergangenheit öffentlich positive Bemerkungen zu Foveros gemacht, was Intels Technologien zusätzlich Glaubwürdigkeit verleiht. Ob sich dieses Lob in kommerzielle Volumenaufträge übersetzt, hängt von mehreren Faktoren ab: Herstellkosten, Yield-Optimierung, Integrationsaufwand, Partnerschaftsmodelle und die Fähigkeit, kundenspezifische Anforderungen in industriellem Maßstab zu erfüllen. Dennoch signalisiert solche öffentliche Unterstützung, dass Top-Designer das technische Potenzial von Intels Ansatz anerkennen.

Für TSMC und andere Foundries bedeutet das Szenario eine Weckruf: Die weitere Skalierung von Advanced Packaging-Kapazitäten, flexible Preisgestaltung und gezielte Partnerschaften werden entscheidend sein, um Marktanteile zu halten. Gleichzeitig erhöht sich die Bedeutung von Interoperabilität, Standardisierung (z. B. für Chiplet-Interconnects) und Testinfrastruktur, damit Kunden nahtlos zwischen verschiedenen Packaging-Optionen wechseln können.

Worauf man als Nächstes achten sollte

- Neue Partnerschaften oder Wafer- bzw. Package-Level-Liefervereinbarungen zwischen Intel und großen Designern — solche offiziellen Deals weisen auf eine konkrete Verschiebung in der Supply-Chain hin.

- Ankündigungen von Produktdesigns oder Referenzplattformen, die explizit EMIB oder Foveros in ihren Packaging-Notizen aufführen — Produktdokumentation und technische Teardowns sind oft aussagekräftig.

- Kapazitätsbewegungen bei TSMC — jede Erweiterung, Priorisierungsänderung oder neue Fertigungsplanung beeinflusst, wie schnell Kunden zu alternativen Packaging-Lösungen diversifizieren.

Zusätzlich sollten Beobachter auf Patentaktivitäten, Veröffentlichungen zu Yield-Verbesserungen, Test- und Packaging-Partnerschaften in der Lieferkette sowie akademische und industrielle Forschungsberichte achten. Solche Informationsquellen liefern Kontext zur Reife der Technologien und zur Skalierbarkeit für Serienproduktion.

Advanced Packaging hat sich zu einem zentralen Wettbewerbsfaktor entwickelt, vergleichbar mit Prozessknoten und Transistordichte. Intel's EMIB und Foveros sind zwar keine Allheilmittel, stellen aber glaubwürdige Alternativen dar, die unterschiedliche architektonische Bedürfnisse bedienen. Während Chip-Hersteller die Leistungsgrenzen mit Kombinationen aus Chiplets und gestapelten Dies verschieben, sind Personalaufbau und diskrete Evaluierungen oft Vorboten größerer strategischer Veränderungen.

Für Analysten, Supply-Chain-Manager und Hardware-Architekten ist es sinnvoll, Stellenanzeigen, Partnerschaftsankündigungen und frühe Produkt-Teardowns genau zu beobachten. Diese Signale helfen zu beurteilen, ob Intels Packaging-Technologien den Sprung in den Mainstream schaffen oder ob sie vor allem als ergänzende Optionen in bestimmten Nischen bestehen bleiben. Unabhängig vom Ausgang bleibt klar: Fortgeschrittene Verpackungstechnologien werden die Art und Weise, wie Systeme entworfen und skaliert werden, nachhaltig prägen — und mit ihnen die Wettbewerbsdynamik in der Halbleiterindustrie.

Quelle: wccftech

Kommentar hinterlassen