7 Minuten

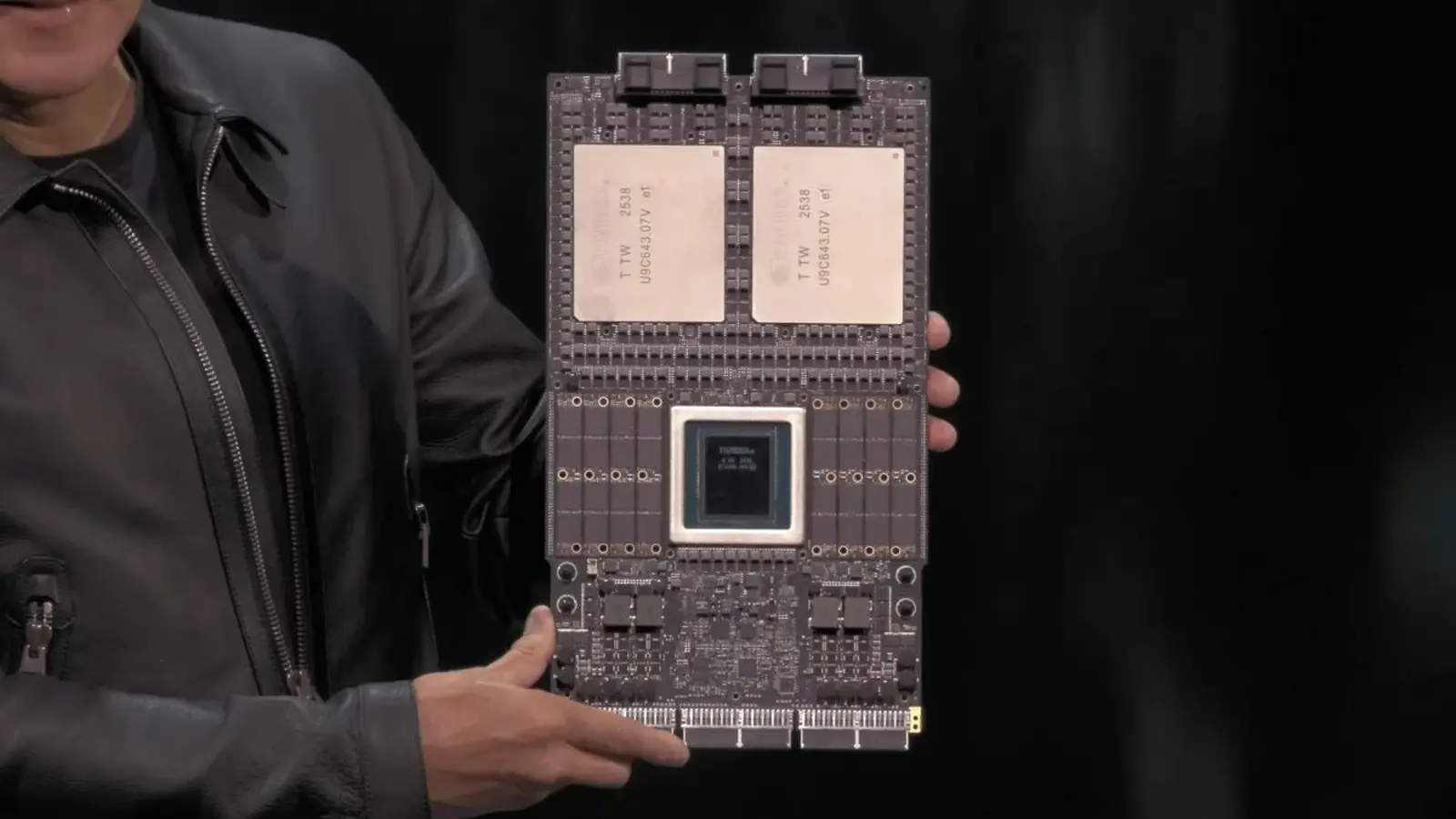

Samsung steht Berichten zufolge kurz davor, eine wichtige Hürde für seine nächste HBM4‑Speichergeneration zu überwinden und von Mustern und Qualifikation in die Serienfertigung überzugehen, die den kommenden Rubin‑KI‑Prozessor von Nvidia sowie andere Anbieter von Beschleunigern beliefern könnte. Diese Entwicklung ist ein strategischer Wendepunkt für Samsung und hat potenziell weitreichende Folgen für den Markt für High‑Bandwidth Memory (HBM), für Lieferketten in Rechenzentren und für die Leistungsfähigkeit moderner KI‑Beschleuniger.

Warum HBM4 für KI wichtig ist

High‑Bandwidth Memory (HBM) stapelt mehrere DRAM‑Würfel (Dies) vertikal und nutzt so eine sehr kurze, aber extrem breite Kommunikationsstrecke zwischen Speicher und Prozessor. Durch diese 3D‑Stapelung und die Verwendung von Through‑Silicon Vias (TSVs), breiten Busse und spezialisierten Interposer‑Techniken erreicht HBM eine deutlich höhere Bandbreite bei geringerem Energieverbrauch pro Bit im Vergleich zu herkömmlichen DDR‑ oder LPDDR‑Modulen. Für KI‑Beschleuniger, die große Modelle, Gewichte und Aktivierungen schnell verschieben müssen, ist eine solche Speicherarchitektur ein entscheidender Leistungsfaktor.

HBM4 stellt dabei den nächsten Generationssprung in Bandbreite, Effizienz und Dichte dar. Verbesserte I/O‑Geschwindigkeiten, optimierte Signalintegrität, geringere Latenzen und bessere Energieeffizienz pro übertragenem Bit sind typische Ziele einer neuen HBM‑Generation. Hersteller von Prozessoren und Beschleunigern ringen darum, Flaggschiff‑Chips mit der jeweils schnellsten verfügbaren HBM‑Technologie zu koppeln, weil Speicherbandbreite und -latenz oft zu den dominierenden Engpässen bei KI‑Training und Inferenz werden. Schlüsselbegriffe in diesem Kontext sind Speicherbandbreite, Speicherlatenz, Energieeffizienz, 3D‑Stapelung und Interposer‑Packaging.

Nachdem Samsung in früheren HBM‑Generationen zeitweise hinter Wettbewerbern zurückgefallen war, signalisiert das HBM4‑Projekt eine mögliche Rückkehr an die Spitze. Branchenberichte deuten darauf hin, dass die neuen Bausteine in bestimmten Bereichen konkurrenzfähiger oder sogar leistungsstärker als vergleichbare Produkte von SK Hynix oder Micron sein könnten. Diese Position wäre strategisch bedeutsam, weil die Speicherperformance direkte Auswirkungen auf die Leistungsfähigkeit kompletter KI‑Systeme hat: Höhere Bandbreite ermöglicht größere Modelle, schnellere Trainingszyklen und effizientere Inferenz in Rechenzentren und Edge‑Systemen.

Zulassung, Zeitplan und weitere Schritte

Laut Bloomberg hat Samsung im September 2025 HBM4‑Muster an Nvidia geliefert und die Bausteine sollen die letzte Phase der Qualifikation erreicht haben. Eine Serienfertigung ist für Februar 2026 geplant; wenn dieser Zeitplan eingehalten wird, könnte Samsung rasch zu einem Zulieferer für Nvidia, aber auch für andere Kunden von KI‑Beschleunigern wie AMD oder Google werden. Wichtig ist dabei die enge Verzahnung von Spezifikation, Systemintegration und Qualitätskontrolle: Prozessor‑ und Beschleunigerhersteller führen oft langwierige Tests durch, um thermische Stabilität, Signalintegrität, Fehlerraten und Langzeitzuverlässigkeit zu verifizieren, bevor sie Speicherkomponenten in Serienprodukten einsetzen.

Der Weg Samsungs war dabei nicht frei von Herausforderungen. Frühere HBM‑Generationen wie HBM3 und HBM3E hatten mit Performance‑Fragestellungen zu kämpfen, was zu Überarbeitungen und Neudesigns führte, um die notwendige Freigabe großer Kunden zu erreichen. Einige HBM3E‑Module wurden nur in ausgewählten Nvidia‑Beschleunigern für bestimmte Märkte (beispielsweise China) eingesetzt, was verdeutlicht, wie restriktiv und spezifisch Vendor‑Qualifikationen sein können. Sollte HBM4 nun tatsächlich die finale Freigabe erhalten haben, deutet das darauf hin, dass Samsung die relevanten Probleme gelöst hat — sei es in der Fertigungsqualität, bei den Yield‑Raten, im Packaging‑Prozess oder in der elektrischen Performance der Stacks.

Die Einführung von HBM4 könnte den Memory‑Markt nachhaltig beeinflussen. Ein erfolgreicher Produktionshochlauf würde Samsungs Position in einem Markt stärken, der lange Zeit von SK Hynix und Micron dominiert wurde, und könnte die Lieferketten für die nächste Chip‑Generation wie Nvidias Rubin und vergleichbare AI‑Beschleuniger umstrukturieren. Für Hardware‑Partner und KI‑Entwickler schafft eine größere Auswahl an hochperformantem Speicher stärkeren Wettbewerb, potenziell niedrigere Preise und eine höhere Versorgungssicherheit, was wiederum die Kapazitäten für Training und Inferenz in Rechenzentren verbessert.

Für Rechenzentren und Hyperscaler sind mehrere Aspekte besonders relevant: Verfügbarkeit, Preis pro GB, Bandbreite pro Watt, thermisches Management und langfristige Lieferstabilität. HBM4 adressiert vorrangig Bandbreiten‑ und Effizienzbegriffe, aber der tatsächliche Nutzen hängt davon ab, wie gut Hersteller wie Samsung die Produktion skalieren und wie zuverlässig die Lieferkette funktioniert. Komponenten wie Interposer‑Technologie (z. B. CoWoS oder EMIB‑ähnliche Lösungen), Packaging, Testinfrastruktur und regionale Fertigungsstandorte spielen eine große Rolle für Time‑to‑Market und Kostenoptimierung.

Technisch gesehen sind mehrere Verbesserungen denkbar, die HBM4 attraktiver machen: höhere I/O‑Raten pro Pin, verbesserte Kanalarchitekturen, geringere Bitfehlerraten (BER), fortschrittlichere ECC‑Mechanismen und optimiertes Thermomanagement auf Modul‑ und Systemebene. Darüber hinaus können Optimierungen in den DRAM‑Würfeln selbst, bei Die‑Verbindungen und bei den Die‑Materialien (z. B. dünnere Dies, verbesserte Die‑Adhäsion) die Packungsdichte erhöhen, ohne proportional mehr Wärme zu erzeugen. Diese technischen Fortschritte sind für KI‑Beschleuniger mit sehr hoher Datenbewegung entscheidend, da sie direkt die nutzbare Leistungsfähigkeit von Modellen beeinflussen.

Verschiedene Marktteilnehmer beobachten den Februar 2026 deshalb genau: Beginnt Samsung dann mit der Serienproduktion, wechselt HBM4 von Labor‑Muster‑ und Qualifikationsstadien in die Rechenzentren und Systeme, die moderne KI‑Workloads antreiben. Ein reibungsloser Ramp‑Up würde zudem Signalwirkung haben: Lieferanten, Systemintegratoren und Cloud‑Provider würden die Möglichkeit erhalten, neue Konfigurationen mit höherem Durchsatz und besserer Energieeffizienz zu planen — von Training‑Clustern über inferenz‑optimierte Edge‑Server bis hin zu speziellen Beschleunigerkarten für Supercomputer.

Aus Sicht der Supply‑Chain‑Strategie wäre Samsungs Markteintritt mit HBM4 eine zusätzliche Absicherung gegen Engpässe. Die Nachfrage nach HBM ist in den letzten Jahren rasant gestiegen, da KI‑Modelle in Größe und Komplexität zunehmen. Zusätzliche Produktionskapazitäten reduzieren das Risiko von Lieferknappheit und können den Preisdruck mindern. Gleichzeitig erhöht ein starker Wettbewerber den Druck auf etablierte Anbieter, ihre Roadmaps, Preisstrategien und Produktionskapazitäten anzupassen.

Welche Risiken bleiben? Selbst bei erfolgreicher Qualifikation und Produktionsplanung sind Yield‑Probleme, unerwartete Integrationsfehler mit spezifischen Beschleunigerdesigns, geopolitische Handelsbeschränkungen und logistische Engpässe potenzielle Stolpersteine. Die enge Zusammenarbeit zwischen Speicherherstellern und Plattformpartnern bleibt essenziell, weil Speichertypen wie HBM stark im Systemkontext optimiert werden müssen: Busbreiten, proprietäre Protokollerweiterungen, thermische Limits und systemseitige Board‑Layouts beeinflussen die tatsächliche Leistungsfähigkeit mehr als einzelne Bauteil‑Spezifikationen.

Für KI‑Ingenieure und Architekten bedeutet die Verfügbarkeit von HBM4: neue Optionen bei der Systemauslegung, größere Modelle auf Single‑Node‑Konfigurationen, schnellere Parameterübertragungen zwischen Speicher und Compute sowie potenziell reduzierte Kosten pro Trainingslauf, wenn die Effizienzgewinne und die Wettbewerbssituation zu Preissenkungen führen. Außerdem eröffnet eine weitere HBM‑Quelle die Möglichkeit, spezialisierte Varianten für unterschiedliche Märkte zu entwickeln — etwa Varianten mit Fokus auf höchste Bandbreite für Training oder auf Energieeffizienz für inferenznahe Applikationen.

Zusammenfassend lässt sich sagen: Sollte Samsung wie berichtet im Februar 2026 in die Massenfertigung von HBM4 starten, wäre das ein markantes Signal für die Branche. Die HBM4‑Ära würde damit den Übergang von Prototypen und Tests in die produktive Nutzung in Rechenzentren markieren und könnte die Speicherlandschaft zugunsten einer stärkeren Konkurrenz, höherer Innovationsdynamik und besserer Versorgungslage verändern. Beobachter aus der KI‑ und Halbleiterbranche sollten deshalb sowohl technische Benchmarks als auch Lieferketten‑Signale in den kommenden Monaten genau verfolgen.

Quelle: sammobile

Kommentar hinterlassen