10 Minuten

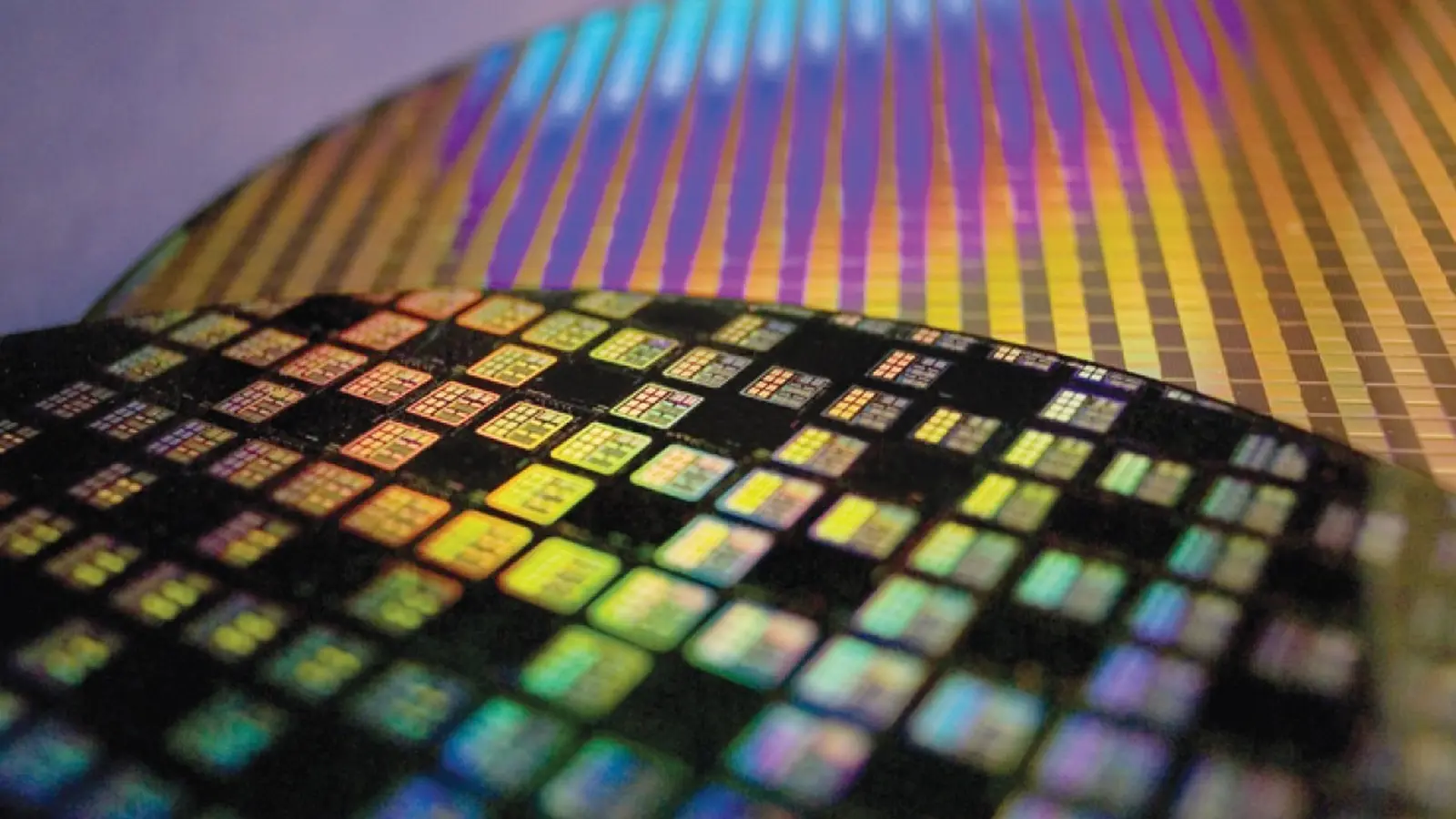

TSMCs Umstieg auf die 2‑nm‑Fertigung beginnt die Wirtschaftlichkeit von Smartphone‑Flaggschiffen neu zu formen. Neue Transistorarchitekturen wie GAA‑Nanosheets und weiterentwickelte Packaging‑Verfahren versprechen höhere Leistung bei besserer Energieeffizienz. Gleichzeitig führen anfängliche Fertigungsherausforderungen, höhere Materialkosten und intensive Investitionen in Forschung und Anlagen jedoch bereits zu spürbaren Kostensteigerungen – und ein Großteil dieser Mehrkosten könnte letztlich bei den Käuferinnen und Käufern landen.

Warum 2nm‑Chips so teuer werden

Samsung hat bereits den Exynos 2600 als erstes Produkt mit 2‑nm‑Technik für die Galaxy S26‑Serie herausgestellt, doch Apple, Qualcomm und MediaTek ziehen schnell nach. Apples A20 für das iPhone 18, Qualcomms Snapdragon 8 Elite Gen 6 und MediaTeks Dimensity 9600 werden erwartet, auf TSMCs N2‑Node gefertigt zu werden, während der Foundry die Kapazitäten für die Massenproduktion hochfährt.

Ein aktueller Bericht der Taiwan Economic Daily News nennt mehrere Treiber, die die Herstellungskosten in die Höhe treiben und damit den Stückpreis von High‑End‑SoCs und daraus resultierend den Preis von Premium‑Smartphones beeinflussen:

- Niedrige Ausbeuten in der ersten Generation. Die neuen Gate‑All‑Around (GAA) Nanosheet‑Transistoren liefern auf dem Papier deutliche Vorteile bei Schaltleistung und Leakage, sind in der Fertigung aber anspruchsvoll. In frühen Produktionsläufen fallen mehr Wafer und Pakete bei Qualitätsprüfungen durch, was die effektiven Kosten pro funktionalem Chip erhöht.

- Komplexes Packaging. Neue Packaging‑Techniken, die für 2‑nm‑Chips notwendig sind – etwa fortgeschrittenes 3D‑Stacking, interposerbasierte Lösungen oder feinere Substrate für höhere I/O‑Dichte – fügen zusätzliche Fertigungsschritte und Materialkosten hinzu. Solche Prozesse müssen in den Fabs in Hsinchu und Kaohsiung erst stabilisiert werden.

- Druck auf Komponentenpreise. Engpässe im Speicherbereich haben die Preise für DRAM und schneller UFS‑Flash‑Speicher nach oben gedrückt; auch andere Bauteile folgen dem Trend, was die gesamte Stückliste (Bill of Materials) für Flaggschiff‑Geräte verteuert.

- Forschungs‑ und Kapitalintensität. Der Wechsel zu N2 erfordert enorme Investitionen in Lithographie, Mess‑ und Prüfgeräte (insbesondere EUV‑Tools von Anbietern wie ASML), IF‑Fertiger für Packaging und umfangreiche R&D. Diese Kosten werden typischerweise entlang der Lieferkette weitergegeben.

Der Report nennt eine markante Zahl: Der A20‑Chip könnte in der Fertigung bis zu 280 US‑Dollar pro Einheit kosten, was einem Anstieg von rund 80 % gegenüber dem A19 entspricht, das im iPhone‑17‑Modell verwendet wurde. Zwar werden für Qualcomm oder MediaTek keine exakten Preise genannt, aber es wird allgemein erwartet, dass deren Spitzenmodelle ebenfalls teurer ausfallen als die Vorgänger.

Welche unmittelbaren Folgen hat das für Konsumentinnen und Konsumenten? Smartphone‑Hersteller können kurzfristig einen Teil der Mehrkosten über marginal reduzierte Margen oder Umverteilungen innerhalb der Stückliste auffangen. Langfristig ist jedoch die wahrscheinlichste kurzfristige Folge ein Anstieg der Verkaufspreise für Premiummodelle – besonders bei Top‑Konfigurationen mit mehr RAM und großem Flash‑Speicher ist mit deutlich höheren Preisaufklebern zu rechnen.

Langfristig normalisieren sich Fertigungsprozesse oft: Ausbeuten verbessern sich, und die anfänglichen Aufschläge flachen ab, sobald die Fabriken die Nanosheet‑Produktion und das Packaging stabilisieren. Für diese erste Generation an 2‑nm‑Geräten und in den Monaten, in denen die Fabs Prozesse verfeinern, ist jedoch mit einem spürbaren Preisaufschlag für die durch 2‑nm‑Technik erzielten Leistungs‑ und Effizienzgewinne zu rechnen.

Beobachter sollten in den kommenden Quartalen insbesondere Yield‑Berichte von TSMC sowie Produktankündigungen von Apple, Qualcomm und MediaTek im Auge behalten. Diese Signale zeigen, wie schnell sich die Ökonomie von N2 normalisiert und ob die Preise für Flaggschiffe stabil bleiben oder weiter steigen.

GAA‑Nanosheet: Technische Details und Herausforderungen

Die Gate‑All‑Around‑Architektur ersetzt in der 2‑nm‑Ära traditionelle FinFET‑Layouts durch Nanosheets, bei denen der Gate‑Kontakt das Kanalmaterial nahezu vollständig umschließt. Dieser Aufbau ermöglicht eine bessere Steuerbarkeit des Kanals, höhere Schaltgeschwindigkeiten und geringere Leckströme. Aus Sicht der Chip‑Designs führt GAA zu einer besseren Performance‑pro‑Watt‑Bilanz, was besonders in mobilen Geräten mit beschränkter Thermik und Batteriekapazität wichtig ist.

In der Fertigung sind Nanosheets jedoch sensibler gegenüber Variationen in Dicke, Interface‑Roughness und Materialspannung. Die Layer‑Stack‑Kontrolle, atomare Ebenen für Gate‑Dämmstoffe und Präzision bei Epitaxie‑Prozessen verlangen enge Prozessfenster und umfangreiche Inline‑Kontrollen, was die Durchlaufzeiten erhöht und die anfänglichen Yieldraten reduziert.

Für OEMs und SoC‑Designer bedeutet das: mehr Testvarianten, zusätzliche Binning‑Stufen und komplexere Qualitätsprüfungen – alles Faktoren, die den effektiven Stückpreis eines funktionierenden Chips erhöhen.

Advanced Packaging: Warum Verpackung jetzt teurer wird

Die reine Die‑Miniaturisierung ist nur ein Teil der Geschichte. Moderne SoCs kombinieren mehrere Compute‑Blöcke, AI‑Beschleuniger, ISP‑Module und Security‑Coprocessoren, die oftmals heterogen gefertigt werden. Um hohe Bandbreiten und niedrige Latenzen zwischen Komponenten zu erreichen, setzen Hersteller auf fortgeschrittene Packaging‑Methoden wie CoWoS, InFO, 2.5D‑Interposer oder sogar 3D‑Stacking mit Through‑Silicon Vias (TSVs).

Solche Lösungen erhöhen die effektive Chipdichte und ermöglichen schnellere Verbindungen, verursachen aber zusätzliche Fertigungs- und Materialkosten: teurere Substrate, zusätzliche Testschritte, komplexere Wärmeableitungslösungen und höhere Ausschussraten bei frühen Implementierungen. Gerade beim Übergang zu 2‑nm‑Knoten sind diese Packaging‑Verfahren oft erst in der Reifephase, wodurch ihre Kosten noch über dem späteren Normalniveau liegen.

Speicher, Peripherie und BOM‑Druck

Ein Flaggschiff‑Smartphone besteht nicht nur aus dem SoC; Speicher (LPDDR5X/LPDDR6), UFS‑Speicher, Kameramodule mit höherer Auflösung, OLED‑Panels mit schnellerer Refresh‑Rate und größere Batterien tragen alle zur Stückliste bei. Wenn DRAM‑ oder NAND‑Preise steigen, wirkt sich das prozentual stärker auf Modelle mit großen Speicherkonfigurationen aus. Hinzu kommt, dass einige neue Features – zum Beispiel integrierte Neural‑Processing‑Einheiten mit großem On‑Chip‑SRAM oder spezialisierte ISP‑Puffer – die SoC‑Fläche vergrößern und damit die per‑Unit‑Kosten weiter erhöhen können.

In Summe führt das zu einem doppelten Druck: erhöhte SoC‑Fertigungskosten plus höhere Kosten für kritische Komponenten, die zusammen die Endkundepreise treiben.

Wie Hersteller die Mehrkosten abfedern können

Smartphone‑Hersteller haben mehrere Hebel, um Preissteigerungen zu mildern, darunter:

- Margen reduzieren: Kurzfristige Reduktion der eigenen Margen, um Preisanstiege für Kunden zu dämpfen. Das ist aber nur begrenzt tragbar und kann die Profitabilität mindern.

- Produktdifferenzierung: Feature‑Segmentation stärker nutzen, teurere Komponenten nur in Top‑Modellen verbauen und Basismodelle preislich attraktiver halten.

- Optimierte BOM‑Gestaltung: Speicher‑ und Displaykonfigurationen anpassen, Suppliers konsolidieren und vermehrt auf kosteneffiziente Module setzen.

- Supply‑Chain‑Verträge: Langfristige Abnahmeverträge mit Speicherherstellern oder gemeinsamen Investitionen in Packaging‑Kapazitäten können Preisstabilität bringen.

All diese Maßnahmen haben Grenzen: Unternehmen müssen konkurrenzfähig bleiben und gleichzeitig die Produktqualität und Innovationskraft bewahren.

Auswirkungen auf Endkunden: Wer zahlt letztlich mehr?

Die unmittelbare Auswirkung ist eine erhöhte Wahrscheinlichkeit für höhere Preisschilder bei Premium‑Flaggschiffen. Kunden, die auf das neueste iPhone‑, Galaxy‑ oder Snapdragon‑basierte Spitzenmodell bestehen, werden wahrscheinlich den größten Preisanstieg spüren, insbesondere bei Versionen mit viel RAM und großem Flash‑Speicher. Für preisbewusste Käufer könnten Hersteller vermehrt Mittelklasse‑Varianten anbieten, die zwar auf die 2‑nm‑SoCs verzichten, aber ein attraktives Preis‑Leistungs‑Verhältnis liefern.

Zudem könnten Händlerpreise, Finanzierungskonditionen und Subventionen (z. B. bei Vertragsabschlüssen) kurzfristig angepasst werden, um die Absatzdynamik zu steuern. Dennoch gilt: wenn die Fertigungskosten dauerhaft höher bleiben, ist eine sukzessive Preisanpassung auf Hersteller‑ oder Händlerebene wahrscheinlich.

Zeitlicher Ausblick: Wann normalisieren sich die Kosten?

Historisch gesehen folgt auf eine neue Prozessgeneration ein typischer Zyklus: anfängliche teure Ramp‑Up‑Phase mit niedrigen Ausbeuten, dann sukzessive Verbesserungen bei Yield und Kosten, bis die Technologie in die Breite skaliert. Bei 2‑nm hängt die Geschwindigkeit der Normalisierung von mehreren Faktoren ab:

- TSMCs Investitionen in zusätzliche N2‑Fertigungskapazitäten und die Geschwindigkeit, mit der neue Linien in Hsinchu und Kaohsiung in Serie gehen.

- Verbesserungen in der Prozesskontrolle für GAA‑Nanosheets und Stabilisierung des Packaging‑Ökosystems.

- Verfügbarkeit und Preise von kritischen Materialien und Equipment, insbesondere EUV‑Reserven und spezialisierte Substrate.

Praktisch gesehen dürften die größten Preisspitzen innerhalb der ersten 2–4 Produktionsquartale auftreten; danach ist eine graduelle Abflachung möglich, aber vollumfängliche Kostennormalisierung kann je nach Nachfrage und Investitionsentscheidungen 12–24 Monate oder länger dauern.

Strategische Bedeutung für den Halbleitermarkt

Die Einführung von 2‑nm‑Technik hat nicht nur kurzfristige Preisimplikationen, sondern verschiebt auch strategisch die Wettbewerbssituation: Wer frühzeitig produktionsfähige 2‑nm‑Designs mit hohem Yield und effizientem Packaging liefert, kann sich langfristig technologische Vorteile bei Performance und Energieeffizienz sichern. Das betrifft nicht nur Apple oder Qualcomm als SoC‑Designer, sondern auch die Zulieferer für Packaging, Testdienstleister und Speicherhersteller, die in die 2‑nm‑Ökonomie integriert werden müssen.

Darüber hinaus erhöht die Kapitalintensität die Eintrittsbarrieren für neue Foundries und stärkt bestehende Marktführer wie TSMC, die über die nötigen Ressourcen verfügen, um den Übergang zu stemmen.

Was Anleger und Branchenbeobachter beachten sollten

Für Analysten und Investoren sind mehrere Indikatoren wichtig, um die Entwicklung der 2‑nm‑Ökonomie zu verfolgen:

- Yield‑Reports und Produktionsmeldungen von TSMC — zeigen sie steigende Ausbeuten und sinkende Fehlerraten?

- Produktankündigungen und Preisgestaltung von Smartphone‑Herstellern — spiegeln Launch‑Preise die höheren Fertigungskosten wider?

- Preisentwicklungen bei DRAM, NAND und spezialisierten Packaging‑Werkstoffen — wie stark treibt das die BOM‑Kosten?

- Investitionspläne von TSMC, ASML und Package‑Anbietern — deuten sie auf schnellere Skalierung hin?

Diese Faktoren zusammen geben Aufschluss darüber, ob die steigenden Kosten temporär sind oder Teil einer längerfristigen Verschiebung in der Kostenbasis der Mobilfunkbranche.

Fazit: Kurzfristige Preisanstiege, langfristige Chancen

Die 2‑nm‑Technologie ist ein bedeutender technologischer Fortschritt mit klaren Vorteilen für Leistung und Energieeffizienz in mobilen Geräten. Kurzfristig bringt der Übergang zu N2 jedoch höhere Fertigungskosten, komplexeres Packaging und Druck auf Komponentenpreise, was die Endkundenpreise für High‑End‑Smartphones nach oben treiben kann. Auf längere Sicht sollten Verbesserungen bei Ausbeute und Prozessreife sowie Skaleneffekte die Kosten relativieren und die breite Verfügbarkeit von 2‑nm‑Vorteilen ermöglichen.

Wer die Preisentwicklung beobachten will, sollte insbesondere Yield‑Meldungen von TSMC, Partnerschaften im Packaging‑Ökosystem und die Preisstrategien der großen SoC‑Designer (Apple, Qualcomm, MediaTek) in den nächsten Quartalen genau verfolgen. Diese Signale zeigen, wie schnell sich die Ökonomie von 2‑nm normalisiert und ob Premium‑Smartphones dauerhaft teurer werden oder sich die Preise mittelfristig stabilisieren.

Zusammengefasst: 2‑nm bringt substanzielle technische Vorteile, aber die Kostenrechnungen in der Anfangsphase können die Preise am Markt nach oben drücken — ein kurzfristiger Preis für eine langfristige Leistungssteigerung.

Quelle: gsmarena

Kommentar hinterlassen