7 Minuten

Ein US-Startup, das vom Gates Frontier Fund von Bill Gates unterstützt wird, hat einen experimentellen KI-Prozessor vorgestellt, der statt mit Elektronen mit Licht arbeitet. Neurophos behauptet, sein optischer Chip könne erhebliche Fortschritte bei Leistung und Energieeffizienz liefern und verspricht damit einen alternativen Ansatz, um die Skalierung von künstlicher Intelligenz jenseits traditioneller Silizium-GPUs voranzubringen.

Von Elektronen zu Photonen: eine andere Art zu rechnen

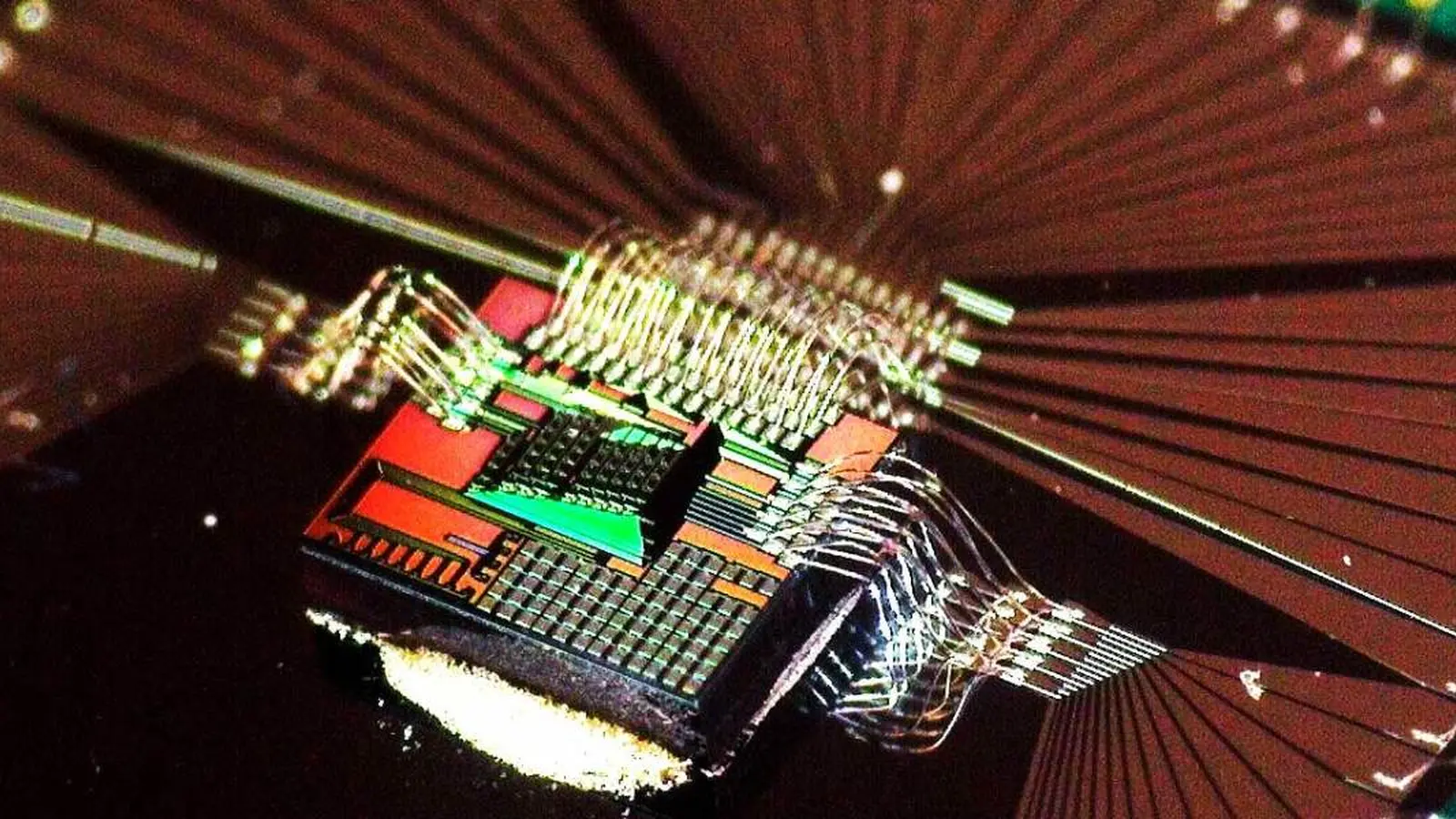

Anstatt Elektronen durch Transistoren zu leiten, führt das Design von Neurophos Berechnungen mit Photonen durch. Licht schaltet schneller und erzeugt deutlich weniger Wärme als der Transport von Ladungsträgern durch Silizium, was theoretisch deutlich höhere Durchsatzraten und einen geringeren Energieverbrauch ermöglicht. Die Firma gibt an, ein zentrales Hindernis für das optische Rechnen überwunden zu haben, indem sie optische Komponenten so weit verkleinert hat, dass ihre Dichte mit den Prozessen bestehender Chipfabriken kompatibel ist. Statt vieler kleiner elektronischer Kerne setzt Neurophos demnach auf eine einzige, sehr große optische Rechenmatrix auf einem Chip. Das wirft Fragen zur Architektur und zum Design auf: Welche Arten von Wellenleitern, Modulatoren und Detektoren kommen zum Einsatz, wie skaliert die Signalqualität mit zunehmender Matrixgröße, und wie werden Präzision und Rauschen bei analogen photonischen Operationen kontrolliert?

Technisch gesehen basiert das optische Rechnen häufig auf der Manipulation von Photonenintensitäten und -phasen, um gewichtete Summen und Matrix-Vektor-Multiplikationen zu realisieren – grundlegende Bausteine neuronaler Netze. Photonische Bauelemente wie integrierte Wellenleiter, Phasenmodulatoren oder mikroring-Resonatoren erlauben die Durchführung linearer Algebra-Operationen mit sehr geringer Verzögerung und ohne die Joulesche Verlustwärme, die in elektronischen Schaltungen unvermeidlich ist. Dennoch bringt dieser Ansatz neue Herausforderungen mit sich: Die Präzisionskontrolle analoger Signale, Kalibrierung gegen Drift, sowie die Anbindung an digitale Steuerlogik für Nichtlinearitäten (z. B. Aktivierungsfunktionen) oder für die hybride Zusammenarbeit mit digitalen GPUs sind komplexe Ingenieursaufgaben. Neurophos sagt, es habe diese Hürden durch eine Kombination aus Miniaturisierung der photonischen Komponenten und cleverer Integration mit klassischen Halbleiterprozessen adressiert, sodass die Herstellung in vorhandenen Foundries denkbar bleibt.

Was das im Vergleich zu heutigen KI-Chips bedeutet

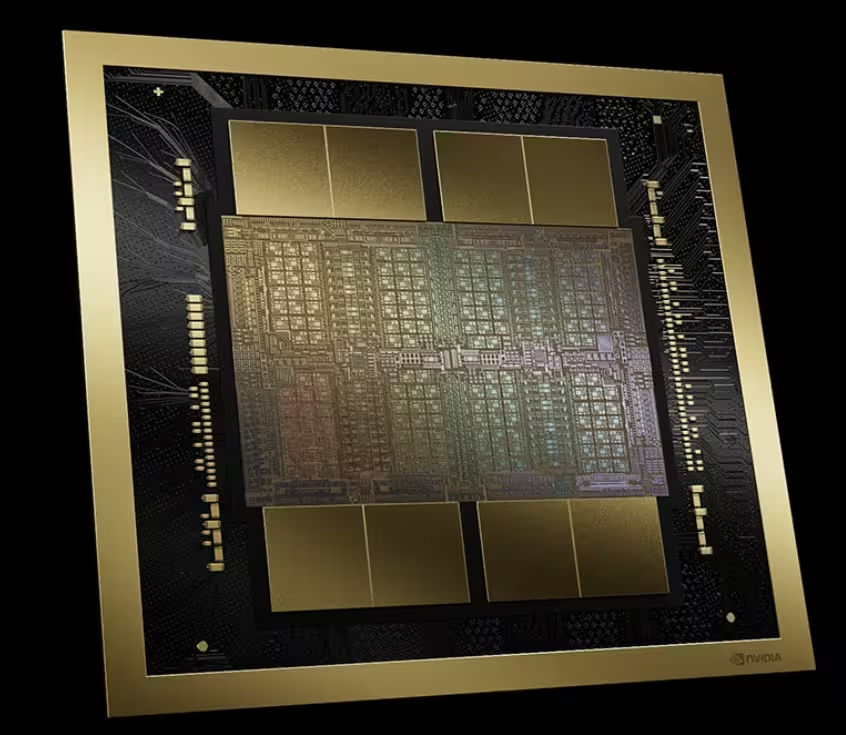

Heutige KI-Beschleuniger von Herstellern wie Nvidia basieren nach wie vor auf elektronischen Schaltkreisen für die grundlegende numerische Mathematik. Nvidia integriert zunehmend photonische Technologien, jedoch primär zur Beschleunigung der Interconnects zwischen Chips oder in Racks — die eigentliche Arithmetik wird weiterhin von Elektronen ausgeführt. Neurophos zielt hingegen auf echtes optisches Rechnen ab, bei dem Photonen die Kern-Matrixoperationen übernehmen, die in neuronalen Netzen dominieren. Sollte sich dieser Ansatz kommerziell und technisch durchsetzen, könnte das die bisherigen Kompromisse zwischen Leistung und Energieverbrauch in Rechenzentren deutlich verändern.

Konkreter heißt das: Für Workloads mit extrem hohen Anforderungen an Matrixmultiplikationen — etwa bei riesigen Transformermodellen, großen Embedding-Berechnungen oder bei latenzkritischen Inferenzpfaden — könnten photonische Beschleuniger deutliche Vorteile bieten. Ihre schnelleren Schaltzeiten und die geringere thermische Verlustleistung würden die Energiekosten pro Operation senken und die Kühlungsanforderungen reduzieren. Gleichzeitig bringt optisches Rechnen Einschränkungen mit sich: Die native Präzision ist oft geringer als die hochpräzisen Gleitkomma-Operationen moderner GPUs; damit wachsen Anforderungen an Quantisierungsstrategien, Fehlerkorrektur und Modell-Anpassung. Ebenso entscheidend sind Software-Stacks und Kompiler, die neuronale Netze so partitionieren und quantisieren, dass sie optimal auf einer photonischen Matrix ausgeführt werden können.

- Schnellere Schaltgeschwindigkeiten: Photonen können Zustände schneller wechseln als Elektronen, was höhere ‚taktartige‘ Raten für bestimmte Operationen ermöglicht und so den Durchsatz bei Matrixberechnungen steigern kann.

- Geringere Wärmeerzeugung: Weniger Verlustleistung reduziert die Anforderungen an Kühlung, senkt die indirekten Energiekosten in Rechenzentren und verbessert die Gesamtenergieeffizienz für großskalige Inferenz- oder Trainingssysteme.

- Dichteres Rechengewebe: Eine einzelne, große optische Matrix kann die Datenbewegung auf dem Chip vereinfachen, weil weniger Daten zwischen vielen verteilten Kernen verschoben werden müssen; das reduziert Latenz und Overhead bei großformatigen linearen Algebra-Operationen.

Reality check: große Hürden bleiben

Trotz der ambitionierten Aussagen steht Neurophos vor Jahren intensiver Entwicklungsarbeit, bevor eine Massenproduktion realistisch wird. Optische Komponenten verhalten sich grundlegend anders als Transistoren: Phasenstabilität, Temperaturabhängigkeit, Fertigungsstreuungen und Kopplungsverluste sind Herausforderungen, die in der klassischen CMOS-Welt so nicht existieren. Zudem müssen Software-Toolchains, Kompiler, Quantisierungsverfahren und Validierungssuites aufgebaut oder angepasst werden, damit Entwickler neuronale Modelle zuverlässig für photonische Beschleuniger optimieren können. Ohne robuste Toolketten ist selbst ein schnellerer Chip nur schwer produktiv nutzbar.

Die Integration in bestehende Rechenzentrumsumgebungen erfordert darüber hinaus Entwicklungen auf Systemebene: Verpackungstechnik für optische Module, Steckverbinder, thermisches Management, Schnittstellen zu bestehenden Server-Stacks und standardisierte APIs für Orchestrierung und Monitoring. Zuverlässigkeitstests im großen Maßstab, Langzeitstabilität und Produktionsausbeute (Yield) sind nichttriviale Risiken, die über wirtschaftlichen Erfolg entscheiden. Daher ist es realistisch zu erwarten, dass photonische Prozessoren zunächst in Nischen und spezialisierten Beschleunigern erscheinen — dort, wo ihr Effizienzvorteil die zusätzlichen Integrationskosten rechtfertigt.

Dennoch signalisiert die Unterstützung durch den Gates Frontier Fund und die Berichterstattung in Fachmedien — zuerst vermeldet von Tom's Hardware — ein wachsendes Interesse an Alternativen zur Silizium-basierten Skalierung. Die Vorstellung kompakter optischer Module, die energiehungrige Inferenz-Racks ersetzen und sowohl Stromkosten als auch Abwärme reduzieren, klingt futuristisch, ist aber technisch plausibel. Startups wie Neurophos treiben diese Vision voran, indem sie sowohl photonische Hardware als auch die begleitenden Softwarekomponenten entwickeln und so das Ökosystem schrittweise erweitern.

Wer gewinnt das Chip-Rennen?

Nvidia bleibt der dominante Akteur mit hoher Wahrscheinlichkeit für die nächsten Jahre, dank einer reifen Software- und Entwicklerökosystems, breiter Hardware-Kompatibilität und massiver Fertigungskapazitäten. Die Marktführerschaft basiert nicht nur auf GPU-Performance, sondern auch auf umfangreichen Bibliotheken, Framework-Integration (z. B. CUDA, cuDNN), Tooling und einem etablierten Ökosystem von Machine-Learning-Ingenieuren. Dennoch könnte das optische Rechnen zu einer starken komplementären Technologie werden: Spezialisierte photonische Beschleuniger könnten für Inferenz oder spezifische, große Matrix-Workloads optimiert werden, während elektronische GPUs weiterhin die allgemeine Ausbildung, flexible Forschung und breite Kompatibilität übernehmen.

Die zentrale Frage ist weniger, ob Nvidia sofort ersetzt wird, sondern wie sich die Hardware-Landschaft für KI in den kommenden zehn Jahren differenziert. Photonische Beschleuniger könnten Performance- und Energiekennzahlen in vielen Anwendungen neu definieren und damit neue Kombinationen aus optischer und elektronischer Hardware provozieren. Eine realistische Entwicklungsspur wäre ein hybrides Rechenzentrum, in dem photonische Module zusammen mit klassischen GPUs koexistieren und jeweils die Aufgaben übernehmen, für die sie am besten geeignet sind. Solche heterogenen Beschleuniger-Stacks verlangen nach Orchestrierungssoftware, die Workloads automatisch teilt, optimiert und zwischen photonischen Matrizen und elektronischen Tensor-Cores verschiebt.

Aus Sicht von Forschung und Industrie liegt die Chance darin, neue Optimierungs- und Kompilierungsmethoden zu entwickeln, Modelle für geringere Präzision zu trainieren und Quantisierungsverfahren zu standardisieren, damit photonische Beschleuniger ihr Potenzial ausschöpfen können. Auf Unternehmensseite werden Investitionen in Fertigung, Verpackung und Ökosystemintegration entscheidend sein. Insgesamt ist die Photoniksparte ein spannender Kandidat, um die nächste Phase der Effizienzsteigerung in der KI-Beschleunigerbranche einzuläuten — doch der Weg dorthin bleibt technisch anspruchsvoll und zeitaufwendig.

Quelle: gizmochina

Kommentar hinterlassen