6 Minuten

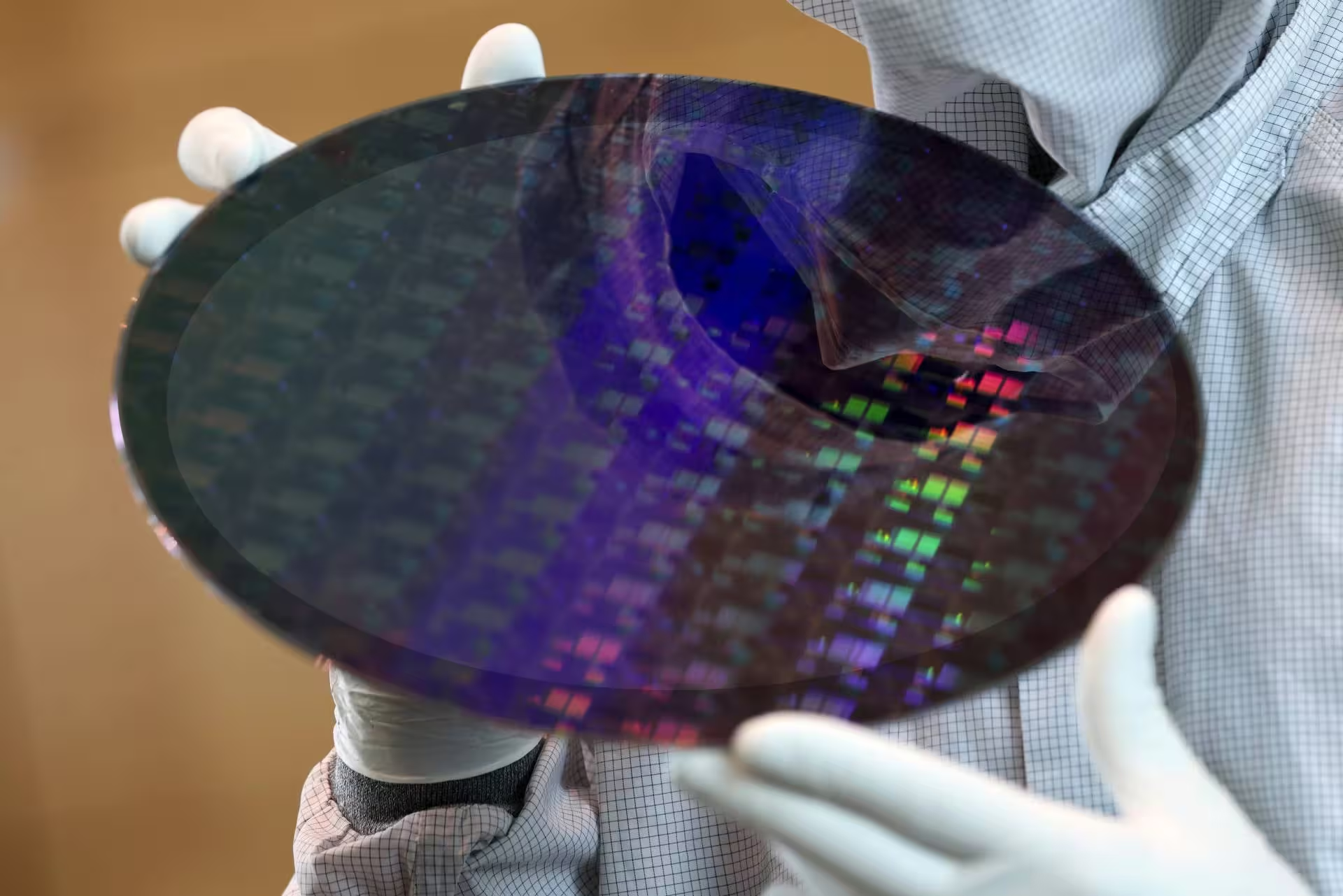

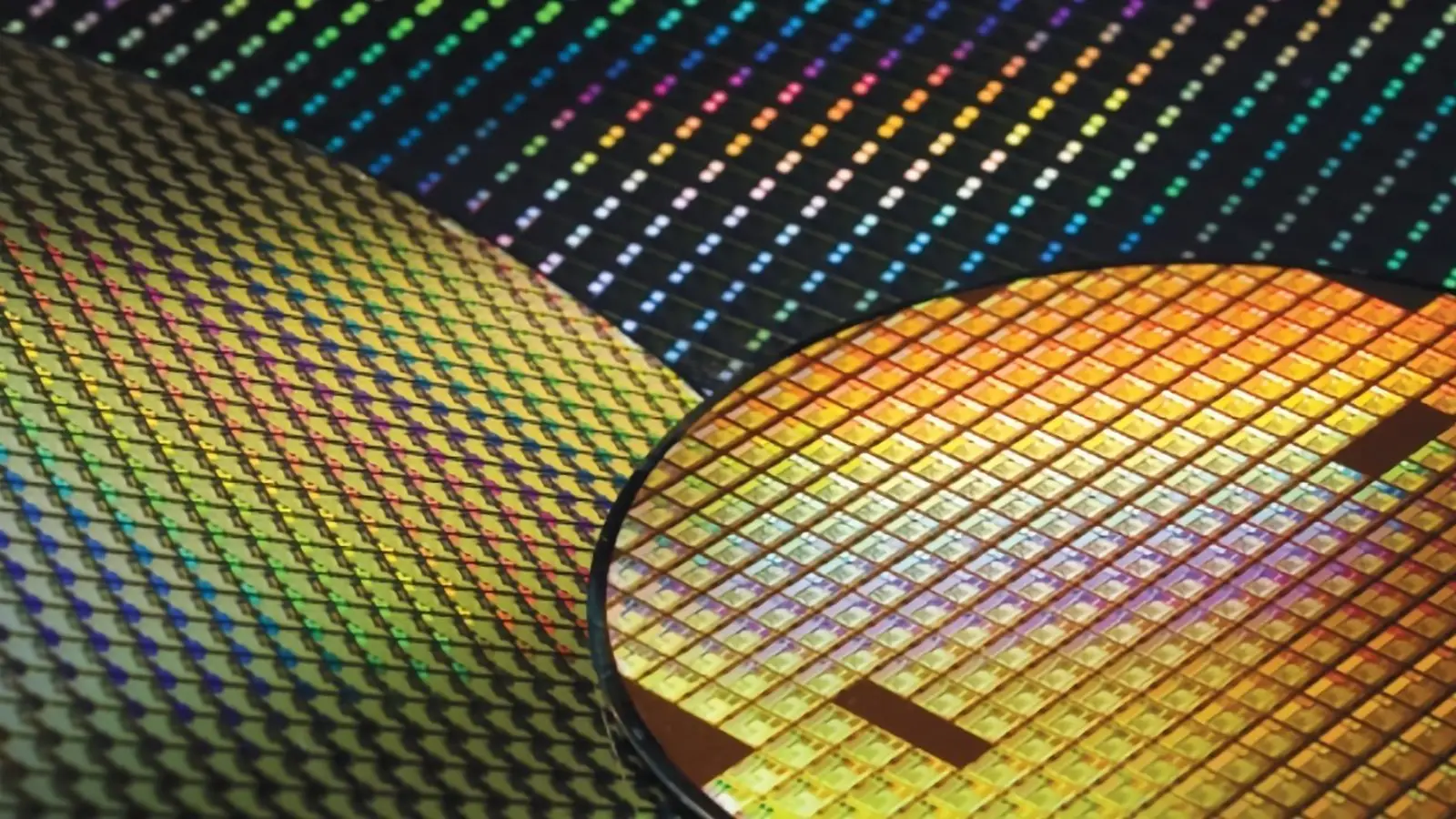

TSMC steht vor einer angespannten Versorgungslage bei 2‑nm‑Wafers, weil die durch Künstliche Intelligenz (KI) getriebene Nachfrage die vorhandenen Kapazitäten an ihre Grenzen bringt. Die Foundry hat ihre Kunden darüber informiert, dass sie ab 2026 über vier aufeinanderfolgende Jahre Preissteigerungen plant — und die erste Runde soll bereits am Neujahrstag in Kraft treten. Diese Mitteilung ist mehr als eine kurzfristige Marktreaktion: Sie spiegelt strukturelle Veränderungen in der Kostenbasis moderner Halbleiterfertigung wider, etwa höhere Ausgaben für High‑NA‑EUV‑Werkzeuge, spezialisierte Prozessentwicklung und qualifiziertes Personal. Für viele Unternehmen bedeutet das erhöhte Stückkosten in frühen Produktionsphasen, potenziell engere Margen in der Einführungsphase neuer Produkte und die Notwendigkeit, Beschaffungs‑ und Finanzpläne frühzeitig anzupassen, um Preissprünge abzufedern und Lieferengpässe zu umgehen.

Warum der Engpass wichtig ist

Die Kapazitäten für TSMCs modernste Nodes sind faktisch bis Ende 2026 gebucht. Dieser Rückstau entsteht hauptsächlich durch eine schnelle Verlagerung von Entwicklungs‑ und Serienaufträgen hin zu Chips, die speziell für KI‑Workloads optimiert sind, also für Inferenz und Training in Rechenzentren ebenso wie für On‑Device‑KI in Smartphones und Edge‑Geräten. Solche Designs erhöhen die Nachfrage nach Wafers, verlängern die Rüstzyklen in den Fabriken und erfordern zusätzliche Fertigungskapazität sowie spezialisiertes Personal für PDK‑Abstimmung, Yield‑Optimierung und Testintegration. Außerdem treiben anspruchsvolle Prozessinnovationen wie Gate‑All‑Around (GAA), Mehrfach‑Patterning und neue Metallisierungstechniken die Komplexität. Die Folge ist ein klassisches „Success‑Problem“: TSMCs technologische Führerschaft macht das Unternehmen zur bevorzugten Foundry, doch die Skalierung zur Befriedigung der schnellen Nachfrage ist zeitaufwändig, kapitalintensiv und anfällig für Engpässe in der Lieferkette.

Branchenanalysten gehen davon aus, dass die Preise für 2‑nm‑Wafers im Jahr 2026 um einen einstelligen Prozentsatz steigen werden, wobei die prognostizierten Werte je nach Forschungsquelle variieren. Einige Analysten nennen eine Bandbreite von etwa 3 % bis 10 % für Preiserhöhungen bei fortgeschrittenen Nodes im kommenden Jahr. Auch der bereits als eng erwartete 3‑nm‑Node von TSMC könnte eine Preiserhöhung von ungefähr 3 % sehen, weil Kunden um begrenzte Fertigungsplätze konkurrieren. Diese Aufschläge lassen sich auf mehrere Faktoren zurückführen: erhöhte Stückkosten während der Ramp‑Up‑Phase, anfängliche Yield‑Volatilitäten, die Notwendigkeit zusätzlicher Prozessschritte und die knappen Kapazitäten bei Vorlieferanten für Spezialchemikalien, Substrate und Testausrüstung. Für OEMs und IDM‑Kunden bedeutet das eine Neubewertung von Preisannahmen, Preiskalkulationen und Zeitplänen — insbesondere wenn Produkte kurz nach Serienstart hohe Stückzahlen benötigen.

Wird diese Situation Käufer zum Rückzug bewegen? Wahrscheinlich nicht. Trotz höherer Preise und der Möglichkeit, auf Samsungs 2‑nm‑GAA‑Prozess auszuweichen, bleiben viele Abnehmer darauf bedacht, ihre Versorgung bei TSMC zu sichern — nicht zuletzt wegen bewährter Ausbeuten, Verlässlichkeit in der Produktion und vorhandenen strategischen Partnerschaften. Das Ergebnis ist eine Verschärfung der Bestandslage: Unternehmen, die nicht frühzeitig Allokationen gesichert haben, sehen sich mit längeren Lieferzeiten und begrenzteren Slots konfrontiert. Parallel dazu reagieren einige Akteure mit taktischen Maßnahmen: Sie verlängern Produktlebenszyklen auf reiferen Nodes, verschieben Teilserien auf Alternativprozesse, setzen verstärkt auf Multi‑Sourcing oder nutzen Packaging‑Ansätze wie Chiplets und SiP (System‑in‑Package), um kritische Funktionalitäten unabhängig von einem einzigen Leading‑Node verfügbar zu machen. Diese Anpassungen sind jedoch keine sofortige Lösung für das zentrale Problem — die physische Knappheit der Fertigungskapazität auf den modernsten Nodes bleibt bestehen.

Apple scheint in diesem Umfeld besonders schnell agiert zu haben: Berichten zufolge hat sich das Unternehmen mehr als die Hälfte der anfänglichen 2‑nm‑Kapazität für hochintegrierte Flagship‑SoCs wie den A20 und A20 Pro gesichert. Eine solche Vorkehrung verschafft Apple potenziell Vorteile bei Leistung, Energieeffizienz und Lieferstabilität für seine nächsten Produktgenerationen. Für Wettbewerber wie Qualcomm und MediaTek bedeutet das jedoch strategische Entscheidungen: Entweder sie akzeptieren geringere Allokationen auf 2 nm und planen Kompromisse bei Volumen und Launch‑Timing ein, oder sie verlagern bestimmte Designs auf alternative Prozessvarianten wie TSMCs N2P (eine auf Performance oder Yield optimierte Variante) beziehungsweise frühere Nodes, die inzwischen ein besseres Kosten‑Nutzen‑Verhältnis bieten. Diese Verschiebungen betreffen nicht nur Smartphones, sondern auch AR/VR‑Geräte, Wearables, Automotive‑SoCs und spezialisierte Edge‑KI‑Beschleuniger — Bereiche, in denen Time‑to‑Market und Energieeffizienz über Markterfolg entscheiden.

TSMC reagiert auf den Druck und investiert in Kapazitätserweiterungen: Das Unternehmen baut mehrere neue Fertigungsstandorte, darunter drei Anlagen mit Fokus auf 2‑nm‑Produktion. Dennoch bleiben Fab‑Bau und Hochlaufzyklen langwierig: Der Aufbau einer neuen Fabrik umfasst Standortauswahl, Genehmigungen, Reinraumkonstruktion, die Beschaffung selten verfügbarer Ausrüstungsgegenstände wie High‑NA‑EUV‑Scanner, die Installation von Deposition‑ und Ätzanlagen sowie umfangreiche Validierungs‑ und Yield‑Optimierungsphasen. Selbst im besten Fall vergehen mehrere Quartale bis Jahre, bis neue Linien stabile Ausbeuten erreichen und die Netto‑Kapazität tatsächlich steigt. Hinzu kommen mögliche Engpässe bei Ausrüstern, Verzögerungen in der Auslieferung kritischer Komponenten, geopolitische Risiken und regulatorische Hürden, die Projekte verlängern können. Kurzfristig ist mit einer graduellen Entspannung zu rechnen, langfristige Entlastung erfordert dagegen kontinuierliche Investitionen und eine robuste, diversifizierte Lieferkette.

Für Gerätehersteller, Chipdesigner und Zulieferer ist die zentrale Botschaft eindeutig: Rechnen Sie mit höheren Foundry‑Kosten und planen Sie Produktionszyklen sowie Budgets entsprechend. Praktische Maßnahmen zur Risikominimierung umfassen Vertragsabschlüsse mit exakter Allokationsplanung, frühzeitige Tape‑Outs zur Priorisierung bei der Kapazitätsvergabe, Multi‑Sourcing‑Strategien, die Entwicklung modularer Architekturen mit Chiplets und SiP, sowie eine verstärkte Optimierung von KI‑Modellen für ressourcenschonendere Implementierungen. Finanzstrategien wie Preis‑Hedging, Lagerhaltung von kritischen Komponenten und frühzeitige Kapazitätsreservierungen werden wichtiger. Außerdem sollten Manager technische Entscheide abwägen: Welche Funktionen rechtfertigen den Einsatz eines Leading‑Edge‑Nodes? Lässt sich die gleiche Systemleistung durch heterogene Integration, spezialisierte Beschleuniger oder Systemoptimierungen auf weniger knappen Nodes erreichen?

Auf Marktebene verdeutlicht der Engpass, wie sehr die KI‑getriebene Nachfrage die Ökonomie der Halbleiterbranche verschiebt: Führende Nodes werden zu strategischen Engpässen, die Wettbewerbsfähigkeit einzelner Unternehmen maßgeblich beeinflussen können. Langfristig dürften Antworten darauf Investitionen in alternative Architekturen, heterogene Integration, spezialisierte Beschleuniger sowie regionale Diversifizierung der Fertigung umfassen. Kurzfristig bleibt die praktische Empfehlung an Hersteller und Entwickler: Prioritäten klar setzen, Kapazitätszuteilungen vertraglich sichern, Entwicklungspläne anpassen und technische Alternativen proaktiv prüfen. TSMC bleibt ein zentraler Akteur im globalen Ökosystem, doch die aktuellen Herausforderungen zeigen, dass technologische Überlegenheit allein nicht ausreicht — es braucht gleichzeitig robuste Fertigungskapazität, stabile Zulieferketten und strategische Partnerschaften, um die nächsten Wellen der KI‑Innovation zu unterstützen.

Quelle: wccftech

Kommentar hinterlassen