9 Minuten

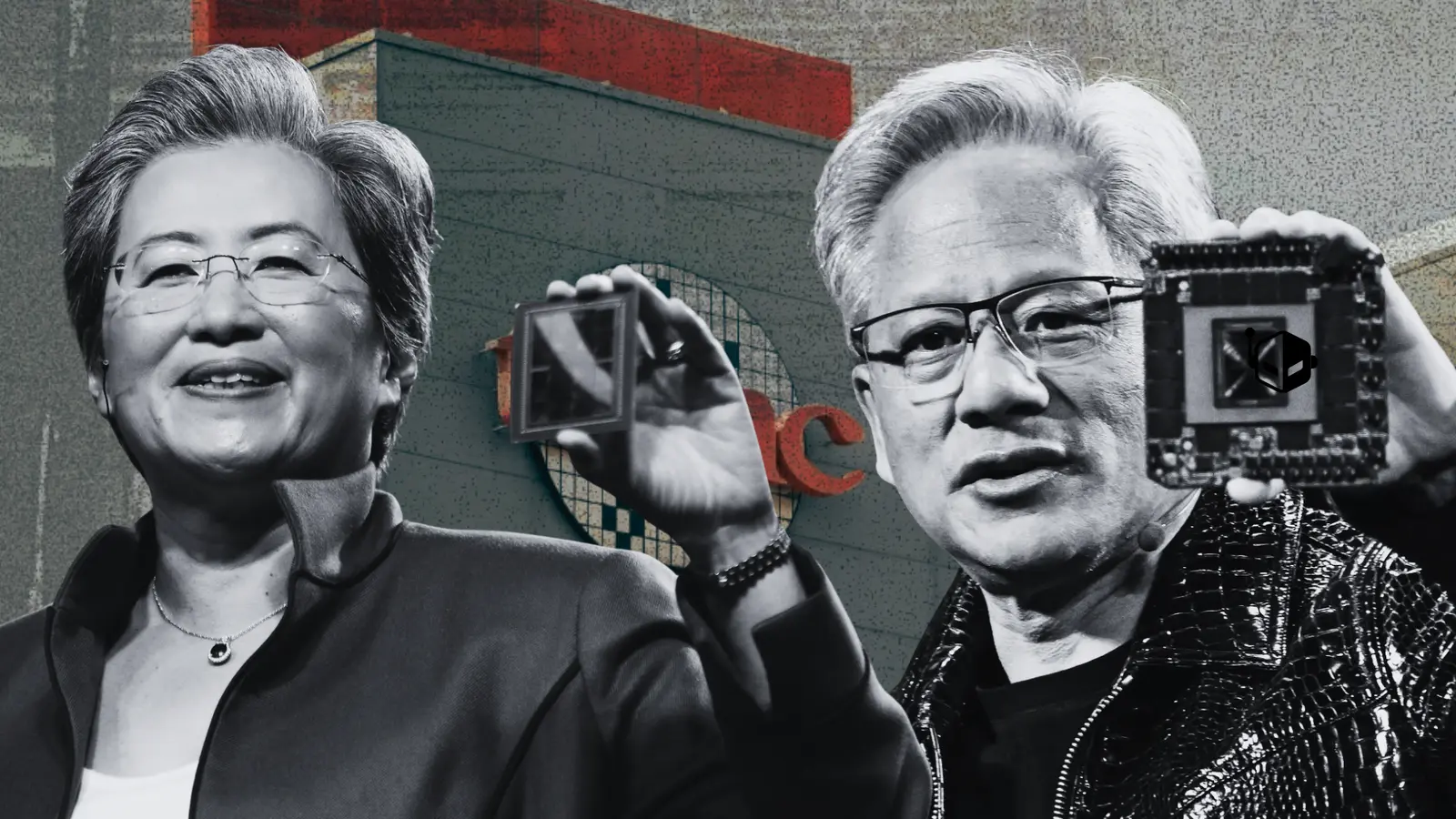

Zwei der einflussreichsten Chiphersteller der letzten Dekade — NVIDIA und AMD — setzten auf TSMC als ihren primären Foundry-Partner. Diese Entscheidung, einst hinterfragt, gilt heute weithin als prägend für die Entwicklung der modernen KI- und Hochleistungsrechner-Landschaft.

Ein Wagnis, das die Chipwelt veränderte

TSMC wurde nicht über Nacht zur Rückgrat der KI-Lieferkette. Gegründet und ausgebaut unter Morris Chang, legte die Foundry lange vor dem öffentlichen Fokus auf KI und Halbleitermangel großen Wert auf Kundenvertrauen und tiefe technische Zusammenarbeit. Für Unternehmen, die sich früh verpflichteten, bedeutete das priorisierten Zugriff auf führende Prozessknoten, gemeinsame IP-Entwicklung und reibungslosere Ramp-ups — Vorteile, die sich als entscheidend erwiesen, als die Nachfrage nach KI-Beschleunigern explosionsartig anstieg.

Jensen Huang hat wiederholt davon berichtet, Morris Chang versichert zu haben, dass NVIDIA ein großer TSMC-Kunde werden würde — ein Versprechen, das in herausfordernden Knoten wie 28 nm mutig wirkte, heute aber als vorausschauend gilt. Diese enge Partnerschaft ermöglichte NVIDIA langfristige Verträge und privilegierten Zugang zu fortschrittlichen Prozessen, was erheblich zur rasanten Entwicklung von Data-Center-GPUs und KI-Beschleunigern beitrug.

Der Schritt von AMD war nicht weniger folgenreich. Unter der Führung von Lisa Su löste sich AMD von traditionellen Fertigungsbindungen und machte nach dem Ausgliedern von GlobalFoundries TSMC zu seinem führenden Hersteller. Diese Neuausrichtung half AMD, Leistungs- und Effizienzdefizite zu schließen, Marktanteile im Serverbereich zu gewinnen und direkter mit Wettbewerbern zu konkurrieren, deren Fertigungsstätten nicht in gleichem Tempo mithalten konnten.

Warum ist das wichtig? Exzellente Fertigung ist ein Nadelöhr im modernen Chipdesign. Überlegene Prozessknoten, Yield-Verbesserungen und planbare Kapazitätsplanung übersetzen sich direkt in Produktleistung und Verfügbarkeit. TSMCs Bereitschaft, langfristige Kundenbeziehungen zu pflegen — statt kurzfristige Umsätze in den Vordergrund zu stellen — schuf ein Ökosystem, in dem Designer Chips an den Stärken eines Nodes optimieren und Versorgung sichern konnten, wenn die Nachfrage stieg.

Intels Probleme mit eigenen Fertigungsprozessen unterstreichen diesen Kontrast. Selbst der traditionsreiche Branchenriese hat für bestimmte Produktlinien auf TSMC zurückgegriffen, was zeigt, wie die Wahl des Foundrys strategisch über Sieg oder Niederlage im Halbleitergeschäft entscheiden kann.

Heute, in einer Zeit, in der die Branche über Kapazitäten und Geopolitik debattiert, ist die praktische Lehre klar: frühzeitige, vertrauensbasierte Partnerschaften mit einem führenden Foundry können die Roadmap eines Chipherstellers vervielfachen. NVIDIA und AMD kauften nicht nur Wafer — sie investierten in eine Beziehung, die mit den Anforderungen der KI mitwuchs. Die Rendite zeigt sich in schnelleren Produkt-Rollouts, privilegiertem Prozesszugang und dem Marktmomentum, das beide Firmen heute genießen.

Warum die Foundry-Wahl strategisch entscheidend ist

Die Entscheidung für einen Foundry-Partner beeinflusst praktisch alle Aspekte der Chipentwicklung — von der frühen Architektur über Validierung und Test bis zur Massenproduktion. Wichtige Einflussfaktoren sind:

- Technologischer Vorsprung bei Prozessknoten (z. B. 7 nm, 5 nm, 3 nm),

- Yield-Verbesserungen und Methodiken zur schnellen Yield-Ramp,

- Verfügbarkeit von Kapazitäten und langfristige Produktionsplanung,

- Fähigkeiten bei Packaging, Chiplet-Integration und InP (integration package) Technologien,

- Ökosystem-Unterstützung, etwa durch EDA-Tool-Integrationen und IP-Partnerschaften,

- Geopolitische Resilienz und Diversifizierung der Lieferketten.

Für fabless Unternehmen wie NVIDIA und AMD ist der Foundry-Partner nicht nur ein Auftragsfertiger, sondern ein technologischer Co-Entwickler. Frühe Design-Technology-Co-Optimierung (DTCO) reduziert NRE-Kosten (Non-Recurring Engineering) pro Design-Iteration und beschleunigt die Zeit bis zur Marktreife.

Prozessknoten und EUV: technische Hebel

Die Einführung von EUV-Lithografie (Extreme Ultraviolet) war ein Wendepunkt für die Skalierung unterhalb von 10 nm. Ein Foundry mit frühzeitiger EUV-Kompetenz kann Aggressivität beim Scaling katalysieren. Das betrifft nicht nur Transistorgrößen, sondern auch FinFET-Optimierungen, Gate-All-Around-Entwicklungen und Packaging-Ansätze wie CoWoS oder InFO für hohe Bandbreiten und Energieeffizienz.

Ein weiterer technischer Hebel ist das Yield-Engineering: Maskensätze (Mask sets), OPC-Optimierungen (Optical Proximity Correction), Test-Methodiken und die Auswertung großer Datenmengen zur Identifikation von Yield-Limiting-Faktoren. Unternehmen, die eng mit ihrem Foundry zusammenarbeiten, profitieren von schnellerer Root-Cause-Analyse und kürzeren Iterationszyklen.

Geschäftsmodell: Fabless gegenüber IDM

Das klassische Modell der integrierten Device Manufacturers (IDM) wie Intel basiert auf eigener Fertigung, während fabless Firmen den Produktionsschritt auslagern. Beide Modelle haben Vor- und Nachteile:

- IDM: Kontrolle über Fertigungsprozess, aber hohe Kapitalbindung, Risiko von Technologieverzögerungen und begrenzte Skalierbarkeit.

- Fabless: Fokus auf Design und SoC-Optimierung, geringere CAPEX-Belastung, jedoch Abhängigkeit von Foundry-Kapazität und Partnerpolitik.

Die jüngere Entwicklung zeigt hybride Ansätze: manche IDM investieren in Foundry-Partnerschaften oder lassen kritische Produkte extern fertigen, um Flexibilität und Zugang zu modernem Prozess-Know-how zu erhalten.

Finanzielle und operative Vorteile langfristiger Verträge

Multi-Jahres-Verträge, gemeinsame CAPEX-Investitionen in Fertigungsanlagen und garantierte Losgrößen reduzieren Planungsunsicherheiten. Für Foundries sind solche Vereinbarungen attraktiv, weil sie Umsatzvorhersehbarkeit schaffen; für Chiphersteller sichern sie Kapazität in einer Zeit, in der Investitionen in neue Wafer-Fabs mehrere Milliarden Dollar und Jahre Entwicklungszeit erfordern.

Fallstudie: NVIDIA — Roadmap, GPUs und KI-Beschleuniger

NVIDIAs starke Marktposition in GPUs und KI-Beschleunigern ist nicht ausschließlich dem Design geschuldet; die enge, strategische Kooperation mit TSMC war genauso entscheidend. Zugang zu frühen Prozessknoten und gemeinsames Engineering ermöglichten aggressive Takt- und Leistungsverbesserungen bei gleichzeitig kontrollierbarem Leistungsverbrauch.

Wesentliche Faktoren waren:

- Frühzeitiger Zugriff auf fortschrittliche Knoten,

- Priorisierte Maskenlaufzeiten und frühe Yield-Optimierung,

- Kooperative Entwicklung von Prozessbibliotheken und IP (z. B. HBM-Interface-Optimierungen),

- Integration von Hochbandbreiten-Speicherlösungen und Paketierungstechnologien für Data-Center-Anwendungen.

In Kombination führte das zu schnelleren Produktzyklen, höherer Energieeffizienz pro Rechenleistungseinheit und damit zu einem deutlichen Wettbewerbsvorteil beim Bereitstellen skalierbarer KI-Infrastruktur.

Fallstudie: AMD — Vom Prozessorwettbewerb zur Serverrelevanz

AMD gelang mit der strategischen Entscheidung zur Zusammenarbeit mit TSMC eine bemerkenswerte Rückkehr ins Serversegment. Durch Nutzung von TSMCs fortschrittlicher Knoten konnte AMD Leistung pro Watt verbessern und mit Zen-Architekturen und Chiplet-Designs den Abstand zu Konkurrenten verringern.

Die Einführung modularer Chiplet-Architekturen, kombiniert mit TSMCs Packaging-Fähigkeiten, ermöglichte AMD eine skalierbare Produktion mit flexiblen Yield-Strategien und relativ geringeren Risiken beim Übergang auf neue Nodes.

Chiplets und Packaging: neue Dimensionen der Fertigung

Die Abkehr vom monolithischen Die-Design hin zu Chiplets verändert die Produktionsdynamik: Hersteller können heterogene Funktionen (CPU, GPU, I/O) auf separaten Dies optimieren und in fortschrittlichen Verpackungen zusammenführen. Foundries und OSATs (Outsourced Semiconductor Assembly and Test) spielen hier eine zentrale Rolle.

Für Designer bedeutet das mehr Architektur-Flexibilität, aber auch neue Herausforderungen beim Testen, bei der thermischen Auslegung und bei der Signalintegrität zwischen Chiplets. Enge Zusammenarbeit zwischen Designteams, Foundry und Packaging-Partnern wird damit noch wichtiger.

Geopolitik, Kapazität und Resilienz der Lieferkette

Die weltweite Nachfrage nach Halbleitern hat die geopolitischen Aspekte der Fertigungsinfrastruktur in den Vordergrund gerückt. Foundries in verschiedenen Regionen, staatliche Förderprogramme und Investitionen in lokale Fertigungskapazitäten sind Antworten auf das Risiko geopolitischer Spannungen.

Für Chiphersteller ist die Balance zwischen optimiertem Zugang zu Spitzentechnologie (die oft bei wenigen Foundries konzentriert ist) und Versorgungssicherheit zentral. Diversifizierte Produktionsnetzwerke, Back-up-Fertigungspartner und strategische Lagerhaltung von kritischen Komponenten tragen zur Resilienz bei.

Kapazitätsplanung: ein langfristiges Spiel

Der Bau neuer Fabs ist kapitalintensiv und zeitaufwändig. Daher sind Prognosen, Absicherungen durch langfristige Abnahmeverträge und gemeinsame Investitionen essenziell. Unternehmen, die frühzeitig signalisieren, wie viel Kapazität sie benötigen, haben oft bessere Chancen, bevorzugt bedient zu werden.

Technische Details, die oft übersehen werden

Neben Prozessknoten sind mehrere feintechnische Aspekte entscheidend für den Erfolg einer Partnerschaft:

- Maskenanzahl und -komplexität: Mehr Masken bedeuten höhere NRE-Kosten und längere Durchlaufzeiten,

- Design-Rule-Checks (DRC) und Foundry-Design-Kits (PDKs): präzise PDKs und gute Toolchain-Integration beschleunigen die Validierung,

- Testinfrastruktur und Burn-In-Kapazitäten: frühzeitiges und umfangreiches Testen reduziert Ausfälle im Feld,

- Supply-Chain-Koordination für Materialien wie Photomasken, Spezialgase und Si-Wafer.

Solche Details können über Markteinführungstermine und Margen entscheiden, sind aber oft weniger sichtbar in öffentlichen Debatten über Nodes und Market-Share-Zahlen.

Best Practices für Chiphersteller

Unternehmen, die ihre Chancen maximieren wollen, sollten folgende Strategien in Betracht ziehen:

- Frühzeitige, technische Abstimmung mit Foundry-Partnern während der Architekturphase,

- Investitionen in Co-Engineering-Teams, die zwischen Design und Fertigung vermitteln,

- Flexible Produktarchitektur (z. B. Chiplets), die node-agnostisch skaliert,

- Absicherung von Kapazitäten durch kombinierte Allokations- und Vertragsstrategien,

- Aufbau eines diversifizierten Lieferantennetzwerks für kritische Materialien und Testkapazitäten.

Ausblick: Wie sich die Dynamik weiterentwickeln könnte

Die Halbleiterbranche bleibt in einem Zustand beschleunigten Wandels. Wichtige Trends, die die Foundry-Beziehungen weiter prägen werden, sind:

- Weiteres Scaling in Richtung 3 nm und darunter sowie Übergänge zu Gate-All-Around-Technologien,

- Breitere Nutzung von Chiplets und heterogener Integration,

- Stärkere regionale Investitionen in Fabriken, um geopolitische Risiken zu mindern,

- Intensivere Kooperationen zwischen Foundries, EDA-Anbietern und IP-Vendoren zur Verbesserung des Ökosystems.

Diese Entwicklungen sprechen dafür, dass fundierte, langfristige Partnerschaften zwischen Chipherstellern und Foundries weiterhin ein Schlüsselfaktor für Marktführerschaft und Innovationsgeschwindigkeit sein werden.

Fazit

Die frühen Wetten von NVIDIA und AMD auf TSMC zeigen, dass strategische Foundry-Partnerschaften mehr sind als reine Fertigungsentscheidungen. Sie sind Investitionen in Technologie, Kapazität und gemeinsame Roadmaps. Gerade in einem Markt, der durch KI-Beschleunigung und hohe Nachfrage nach Rechenleistung geprägt ist, können solche Partnerschaften über Erfolg und Marktposition entscheiden. Die Lehre für die Branche ist klar: Technologie allein reicht nicht aus — die richtige Fertigungspartnerschaft, frühzeitig und vertrauensvoll gestaltet, ist oft der entscheidende Hebel.

In einer Zeit, in der sich Technologie, Geschäft und Geopolitik überschneiden, bleibt die Fähigkeit, Produktionskapazitäten, technologische Exzellenz und langfristige Partnerschaften zu verbinden, ein entscheidender Wettbewerbsvorteil.

Quelle: wccftech

Kommentar hinterlassen