6 Minuten

Googles neue Ironwood-TPU-Familie hat eine bereits schwelende Auseinandersetzung im Bereich KI-Hardware neu entfacht: Diesmal ist der eigentliche Herausforderer für Nvidia nicht AMD oder Intel, sondern Googles eigene kundenspezifische Siliziumlösung, die gezielt für Inferenz optimiert wurde. Mit beeindruckender Speicherkapazität, dichten Interconnects und aggressiven Effizienzversprechen verändert Ironwood, wie Cloud‑KI in großem Maßstab aussehen kann.

Ironwood nach Zahlen: Speicher, Rechenleistung und ein skalierendes SuperPod

Kernziel von Ironwood (TPU v7) ist ein einziges Szenario – Modelle in Produktion zu betreiben. Google positioniert den Chip als "inference-first"‑Design, dessen Spezifikationen darauf ausgerichtet sind, Latenz zu reduzieren, Energie pro Anfrage zu senken und die Bereitstellung großer Sprachmodelle sowie anderer Echtzeit‑KI‑Dienste zu vereinfachen. Diese Inferenzorientierung unterscheidet die Architektur bewusst vom klassischen Trainingsfokus vieler GPUs.

- Peak FP8-Rechenleistung pro Chip: ~4,614 TFLOPs

- On‑Package‑Speicher: 192 GB HBM3e (etwa 7–7,4 TB/s Bandbreite)

- Pod‑Skalierung: bis zu 9.216 Chips pro SuperPod

- Aggregate Rechenleistung pro Pod: ≈42,5 exaFLOPS (FP8)

- System‑HBM pro Pod: ~1,77 PB

Solche Rohzahlen sind beeindruckend, doch die Geschichte handelt ebenso davon, wie Chips miteinander kommunizieren. Google nutzt ein InterChip Interconnect (ICI) und eine 3D‑Torus‑Topologie, um viele Chips zu einem kohärenten SuperPod zu verbinden. Durch ein Scale‑Up‑Fabric und ein 1,8 PB großes Inter‑Pod‑Netzwerk sollen große Modelle auf schnellem Speicher verbleiben, anstatt Gewichte über langsamere Links hin‑ und herzuschieben. Dieses Design reduziert Netzwerklast, minimiert Datenbewegungen und ist besonders wichtig für LLMs (Large Language Models), die andernfalls häufige und zeitkritische Speicherzugriffe benötigen.

Warum Inferenz die Wettbewerbslandschaft verschiebt

Lange Zeit war das Schlachtfeld das Training: rohe TFLOPs, riesige Speichervorräte und hochoptimierte Kernel waren die zentralen Kriterien — ein Bereich, in dem Nvidia‑GPUs führten. Doch die Ökonomie der KI verschiebt sich. Nachdem Modelle trainiert sind, sind es Milliarden von Inferenz‑Anfragen und nicht Trainingsläufe, die den Alltag dominieren. Das stellt andere Anforderungen: Latenz, Anfrage‑Durchsatz, Energieverbrauch pro Anfrage und Kosten‑Effizienz rücken in den Mittelpunkt.

.avif)

Ironwood ist um genau diese Metriken herum konzipiert. Großer On‑Package‑Speicher reduziert das Chip‑übergreifende ‚Chatter‘ bei riesigen Modellen und senkt so die Latenz. Google spricht von deutlich besseren generationalen Verbesserungen bei Performance und Energieeffizienz (das Unternehmen behauptet etwa 2× Energieeffizienzgewinne gegenüber vorherigen TPU‑Generationen). Für Hyperscaler und Cloud‑Kunden, die rund um die Uhr Inferenzkapazität bezahlen, kann diese Effizienz in erhebliche Kosteneinsparungen übersetzen — sowohl hinsichtlich Stromkosten als auch Serverdichte und Rack‑Effizienz.

Zusätzlich zur Hardware‑Effizienz spielt Softwareoptimierung eine Rolle: Laufzeiten, Quantisierungsstrategien (z. B. FP8), Compiler (wie XLA für TPUs) und angepasste Inferenz‑Frameworks können Latenz weiter senken und Durchsatz steigern. Die Kombination aus spezialisierten Inferenz‑ASICs, optimierter Software‑Toolchain und Netzwerktopologie ist entscheidend, um die Gesamtbetriebskosten (TCO) pro Anfrage zu reduzieren.

Interconnects, SuperPods und Ökosystembindung

Ein weiterer Wettbewerbsvorteil ist die vertikale Integration. Wenn Google Ironwood über Google Cloud anbietet, kann das Unternehmen den gesamten Stack optimieren — Hardware, Netzwerk und Laufzeitumgebung — um die Kosten pro Anfrage zu senken. Der SuperPod‑Ansatz mit dichtem Interconnect und Scale‑Up‑Fabric wurde entworfen, um sehr große Modelle mit weniger Performance‑Penalties zu bedienen, als dies in einem fragmentierten GPU‑Cluster der Fall wäre.

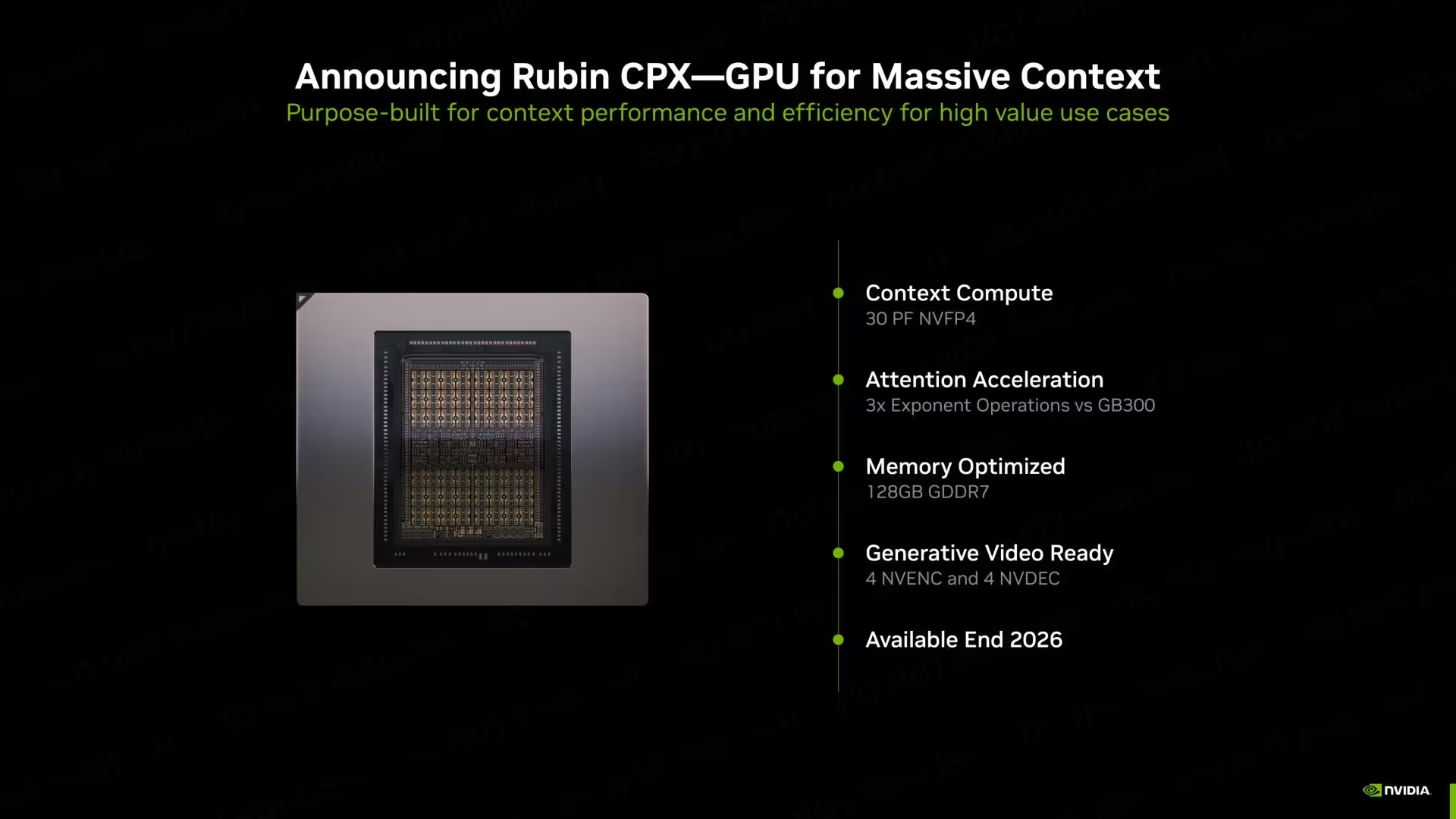

Diese vertikale Integration erhöht zugleich strategische Risiken für Konkurrenten wie Nvidia. Trotz Nvidias Rubin‑Racks und der B200 Blackwell‑GPUs, die gezielt auf Inferenz abzielen, könnten Cloud‑Kunden native TPU‑Infrastruktur bevorzugen, wenn sie messbar geringere Latenz und Betriebskosten bietet. Das Ergebnis wäre eine stärkere Bindung an die Hardware‑Architektur eines bestimmten Cloud‑Anbieters — ein klassischer Lock‑in‑Effekt, der Wechselkosten verursacht und die Marktstruktur langfristig beeinflussen kann.

Für Unternehmen ist die Entscheidung deshalb multidimensional: Neben reiner Performance spielen Portabilität, Ökosystemunterstützung (Frameworks wie TensorFlow, PyTorch, ONNX), Entwickler‑Produktivität und SLAs (Service Level Agreements) eine Rolle. Strategien wie hybride Bereitstellungen (Training auf GPUs, Inferenz auf TPUs) oder Multi‑Cloud‑Architekturen bleiben praxisnahe Optionen, um Abhängigkeiten zu streuen und Ausfallrisiken zu minimieren.

Jensen Huang hat es bemerkt

Der Nvidia‑CEO hat öffentlich eingeräumt, wie schwierig die Entwicklung kundenspezifischer ASICs ist, und TPUs als einen ernstzunehmenden Wettbewerber bezeichnet. Diese Anerkennung ist bedeutsam: Wenn etablierte Marktführer eine rivalisierende Technologie als Bedrohung einstufen, signalisiert das zumeist verstärkte Investitionen und beschleunigte Produktzyklen auf beiden Seiten. Für Kunden bedeutet das: mehr Auswahl, schnellere Innovation und zugleich potenziell volatilere Wettbewerbsbedingungen.

Gleichzeitig verpflichtet das Anbieten eigener ASICs die Cloud‑Anbieter zu umfangreichen Infrastrukturinvestitionen: neue Racks, spezielle Kühlung, geänderte Stromversorgung und angepasste Netzwerkarchitekturen. Solche Investitionen befördern zwar Differenzierung, erhöhen aber auch Eintrittsbarrieren für Neulinge im Markt.

Also, ist Nvidia am Ende?

Keineswegs — aber die Spielregeln verändern sich. Nvidia bleibt führend bei vielseitiger GPU‑Rechenleistung, verfügt über ein riesiges Software‑Ökosystem (CUDA, cuDNN, TensorRT) und ist in vielen Trainingsszenarien sowie in zahlreichen Inferenzanwendungen weit verbreitet. Viele Workloads profitieren nach wie vor von der Flexibilität und Rechenstärke von GPUs. Was Ironwood allerdings öffnet, ist eine neue Wettbewerbsachse, die sich auf Inferenz‑Ökonomie konzentriert: Wie viele Anfragen pro Sekunde kann ein System bei minimalen Kosten und Latenz bedienen?

Für Unternehmen mit großflächigen, latenzsensitiven Produktionsbereitstellungen könnte Googles TPU‑Strategie zum entscheidenden Faktor werden. Gleichzeitig bieten GPUs und spezialisierte Inferenzbeschleuniger wie FPGAs oder andere ASICs weiterhin Vorteile in bestimmten Nischen — etwa bei extremen Trainingsaufgaben, speziellen Berechnungsflüssen oder bei Anforderungen an Portabilität.

Die wahrscheinlichste Entwicklung ist eine koexistente, segmentierte Landschaft: GPUs dominieren Training und flexible Workloads, TPUs und ähnliche Inferenz‑ASICs übernehmen großskalige, latenzkritische Produktionsinferenz. Hybrid‑Architekturen, Orchestrierungstools, Containerisierungslösungen und Interoperabilitäts‑Standards (z. B. ONNX, Trinity zwischen TensorFlow und PyTorch) werden diese Vielfalt handhabbar machen.

Kurz gesagt: Der KI‑Wettbewerb verschiebt sich von „Wer hat die meisten FLOPs?“ hin zu „Wer bedient die meisten Abfragen am schnellsten und günstigsten?“. Mit Ironwood in der Produktion ist zu erwarten, dass Cloud‑Provider, Hyperscaler und Unternehmen neu bewerten, wo sie ihre Inferenz‑Workloads laufen lassen — und das macht Google derzeit zum spannendsten Herausforderer gegen Nvidia.

Aus technischer Sicht bleibt noch viel zu beobachten: die tatsächliche Verfügbarkeit von SuperPods, Benchmark‑Ergebnisse in unabhängigen Tests, Integrationserfahrungen von Kunden und die Entwicklung von Preisstrukturen für High‑Volume‑Inferenz. Ebenso wichtig sind Software‑Ökosysteme und Migrationspfade: Je einfacher es ist, Modelle und Pipelines auf TPUs zu betreiben, desto stärker wird die Adoption ausfallen. In jedem Fall hat Ironwood den Markt angestoßen und die Diskussion über Inferenz‑Ökonomie nachhaltig befeuert.

Quelle: wccftech

Kommentar hinterlassen