9 Minuten

Bericht erklärt, warum einige Galaxy S26-Modelle teurer werden könnten

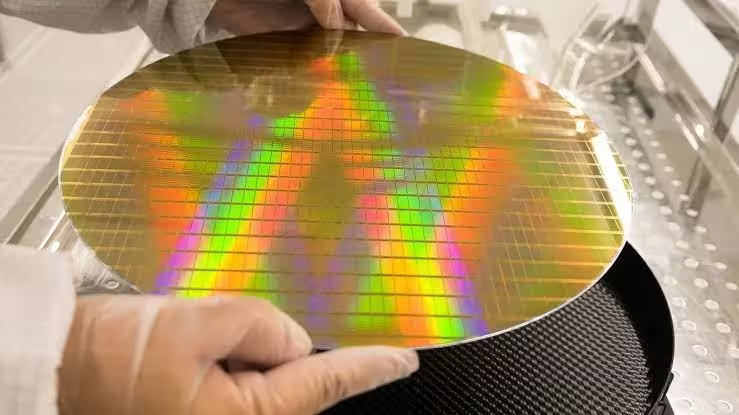

TSMC produziert derzeit hochentwickelte Anwendungprozessoren (APs) im dritten Generationen-3-nm-Prozessknoten (N3P). Derselbe Knoten ist für die Apple A19- und A19‑Pro‑Chips verantwortlich, die das iPhone‑17‑Portfolio antreiben, und wird auch zur Fertigung von Flaggschiff‑APs wie Qualcomms Snapdragon 8 Elite 5 und MediaTeks Dimensity 9500 genutzt. Die fortgeschrittene Fertigung bei 3 nm zielt darauf ab, Leistungsdichte, Energieeffizienz und Taktstabilität zu verbessern, was für Premium‑Smartphones entscheidend ist.

Der Übergang zu kleineren Strukturgrößen bringt allerdings nicht nur technische Vorteile, sondern auch wirtschaftliche Effekte entlang der gesamten Lieferkette. Höhere Fertigungskomplexität, Investitionen in neue Lithographie‑ und Fertigungsanlagen sowie initial niedrigere Erträge bei neuen Nodes treiben die Kosten pro Siliziumwafer nach oben. Diese Kostensteigerungen können sich in mehreren Stufen auf Endkundenpreise auswirken – von Designhäusern über Auftragsfertiger bis hin zu Smartphone‑OEMs.

TSMC erhöht Waferpreise für seinen 3nm‑N3P‑Prozess

Ein Bericht der China Times berichtet, dass TSMC die Preise für Siliziumwafer im N3P‑Verfahren erhöht hat und dass die Chiphersteller diese Kosten weitergeben. Laut dem Bericht zahlt MediaTek etwa 24 % mehr und Qualcomm etwa 16 % mehr für N3P‑Wafer. Der Artikel macht allerdings keine eindeutige Aussage darüber, ob diese Steigerungen relativ zu TSMCs früherer 3‑nm‑Variante (N3E) gerechnet wurden, die bereits für den Snapdragon 8 Elite und den Dimensity 9400 eingesetzt wurde. Diese Differenz könnte Einfluss auf die Margen und Preisgestaltung verschiedener AP‑Generationen haben.

Steigende Waferpreise haben unmittelbare Auswirkungen auf die Chipkosten: Wenn die Fertigung pro Wafer teurer wird, steigt der Stückpreis der fertigen APs, insbesondere in den frühen Produktionszyklen mit noch nicht optimierten Erträgen. Qualcomm und MediaTek, die als Drittanbieter APs an mehrere Smartphone‑Marken verkaufen, müssen einen Teil dieser Mehrkosten tragen oder an ihre Kunden weiterreichen. Das bedeutet: Hersteller von Smartphones, die Chips von Qualcomm oder MediaTek einkaufen, sehen sich mit erhöhten Beschaffungspreisen konfrontiert, was die Wahrscheinlichkeit steigender Endkundenpreise erhöht.

Diese Kaskade von Kosten bedeutet konkret, dass einige Modelle der Galaxy S26‑Reihe mit höheren Verkaufspreisen erscheinen könnten. Insbesondere Varianten, die auf APs basieren, deren Fertigungskosten durch N3P‑Waferpreiserhöhungen stärker belastet wurden, sind gefährdet. Auch andere Geräte wie das erwartete vivo X300, das Berichten zufolge auf dem Dimensity 9500 laufen könnte, wären von ähnlichen Preiserhöhungen betroffen.

Wenn Sie sich fragen, ob Apple ebenfalls höhere Preise für seine 3‑nm‑Wafer bezahlt hat, deutet der China Times‑Bericht darauf hin, dass dies der Fall ist. Apple entwirft jedoch seine eigenen Anwendungprozessoren und beauftragt keine Drittanbieter‑Chiphersteller; das Unternehmen verhandelt direkt mit TSMC. Dieser direkte Beschaffungsweg eliminiert eine Zwischenschicht von Aufschlägen, weshalb Apples Kostenstruktur in der Lieferkette sich von der anderer Smartphone‑Marken unterscheidet, die Chips von Qualcomm oder MediaTek erwerben. Dennoch kann Apple ebenfalls von höheren Fertigungskosten betroffen sein — etwa durch direkte Erhöhungen der Waferpreise oder durch Änderungen bei Kapazitätszuteilungen.

Technisch gesehen liefert der dritte Generationen‑3‑nm‑Knoten voraussichtlich ungefähr einen Leistungszuwachs von rund 5 % bei gleichem Leistungsaufnahme‑Profil oder eine Reduzierung des Energieverbrauchs um 5–10 % bei vergleichbaren Frequenzen. Mit kleineren Prozessknoten schrumpfen die Transistorabmessungen, während die Transistordichte zunimmt – gemessen in Millionen Transistoren pro Quadratmillimeter (MTr/mm²). Eine höhere Dichte ermöglicht in der Regel bessere Single‑Core‑ und Multi‑Core‑Leistung, effizientere Leistungsaufnahme sowie komplexere Integration von Funktionen wie neuralen Beschleunigern, verbesserten GPU‑Slices und integrierten ISP‑Systemen. Aufgrund dieser Optimierungen ist die Dichtemetrik zu einem zentralen Indikator für die Fähigkeiten eines Chips geworden und wird häufig in technischen Spezifikationen und Vergleichen herangezogen.

Zusätzlich beeinflussen Modernisierungen wie EUV‑Lithographie, verbesserte interconnect‑Metallisierung (Back‑end‑of‑Line) sowie die Integration von Chip‑let‑Architekturen (Chiplets) die Kosten und Leistungsfähigkeit moderner APs. All diese Faktoren – Fertigungskomplexität, Yield‑Verbesserungen, Packaging‑Technologien und Materialkosten – werden in die Preisgestaltung einbezogen, wenn Chiphersteller ihre Angebote an OEMs ausrichten.

Erwarten Sie noch höhere Chippreise im nächsten Jahr

Die Preise könnten erneut steigen, sobald TSMC die AP‑Produktion auf seinem 2‑nm‑Node hochfährt. Markt‑Spekulationen deuten darauf hin, dass 2‑nm‑Waferpreise bis zu 50 % über den aktuellen 3‑nm‑Sätzen liegen können, was ein erhebliches Kostensprungrisiko darstellt. Apple hat angeblich ungefähr die Hälfte der 2‑nm‑Kapazität von TSMC reserviert, was die Verfügbarkeit von Fertigungsplätzen für andere große Chiphersteller wie Qualcomm und MediaTek einschränken könnte. Eine solche Kapazitätsallokation kann Marktanteile und Preisverhandlungspositionen verschieben.

TSMC plant angeblich, etwa 60.000 2‑nm‑Wafer pro Monat über vier Fertigungsstätten hinweg zu fertigen. Frühe 2‑nm‑APs könnten zuerst in Premium‑Handsets erscheinen, darunter Modelle wie das Samsung Galaxy S26 Pro und das Galaxy S26 Edge. In vielen Regionen (ausgenommen USA, Kanada und China) könnten diese Modelle mit Samsungs Exynos 2600‑AP ausgeliefert werden, der von Samsung Foundry auf deren 2‑nm‑Node produziert wird. Diese regionale Differenzierung von AP‑Lieferanten ist ein gängiges Marktverfahren, das Preisbildung und Verfügbarkeit weiter beeinflussen kann.

Gate‑All‑Around (GAA) und seine Bedeutung

Sowohl Samsung Foundry als auch TSMC setzen bei ihren 2‑nm‑Nodes auf die Gate‑All‑Around (GAA)‑Transistorarchitektur. GAA baut auf dem FinFET‑Design auf, geht aber einen Schritt weiter, indem das Gate den Kanal vollständig umschließt. Diese Konstruktion minimiert Leckströme, erhöht die Schaltstärke (Drive Current) und verbessert damit die Energieeffizienz und maximale Taktraten. Für mobile APs bedeutet GAA bessere Leistungsverhältnisse und niedrigeren Energieverbrauch bei Spitzenlasten – ein entscheidender Vorteil für Geräte mit hohen Anforderungen an KI‑Workloads, Bildverarbeitung und 5G‑Modems.

GAA bringt jedoch auch neue Design‑ und Fertigungsherausforderungen mit sich: komplexere Masken, präzisere Nanofabrikationsschritte und strengere Kontrollen bei der Materialqualität. Diese technischen Hürden führen zu höheren Entwicklungskosten sowie anfänglich niedrigeren Yield‑Raten, was per Wafer die Kosten weiter erhöht – ein Faktor, der sich mittelbar auf die Preise von APs und letztlich auf die Verbraucherpreise auswirken kann.

Apple wird voraussichtlich seine ersten 2‑nm‑iPhones im nächsten Jahr auf den Markt bringen, ausgestattet mit APs der A20‑Serie. Apples enge Zusammenarbeit mit TSMC und die frühzeitige Reservierung von Kapazitäten verschafft dem Unternehmen oft einen Vorteil bei der Einführung neuer Nodes, sowohl in Bezug auf Zeitplan als auch auf Kosteneffizienz. Für andere Hersteller besteht hingegen das Risiko, später auf die neue Fertigung umstellen zu müssen oder höhere Stückkosten zu tragen.

Blickt man weiter in die Zukunft, plant TSMC die Massenproduktion eines 1,4‑nm‑Nodes für das Jahr 2028, begleitet von einer Namensumstellung von Nanometern auf Ångström (Å). In diesem Schema würde 1,4 nm als A14 (1 nm = 10 Å) bezeichnet. Diese Umbenennung reflektiert den Trend der Branche, neue Maßenamen zu verwenden, da die traditionelle nm‑Bezeichnung weniger direkte Aussagekraft über physische Gate‑Längen und Dichteeigenschaften hat. Nach A14 könnten Unternehmen neue Transistorarchitekturen und alternative Materialien einführen (etwa neuartige Hoch‑k/Metall‑Gate‑Stacks, 2D‑Materialien oder Silizium‑Ergänzungen), um das Mooresche Scaling zu unterstützen und weiterhin Leistungszuwächse zu erzielen.

Neben reinen Strukturgrößen spielen System‑Level‑Veränderungen eine Rolle: Advanced Packaging (CoWoS, FO‑WLP), 3D‑Stapelung und Heterogene Integration (z. B. In‑Package‑Memory, separater NPU‑Chiplet) können Performance‑Gains liefern, ohne allein auf weiter schrumpfende Transistoren zu setzen. Allerdings treiben solche Packaging‑Techniken ebenfalls die Kosten, da sie zusätzliche Materialien, präzisere Fertigungsprozesse und komplexere Prüfverfahren erfordern.

Aus Sicht von Smartphone‑Herstellern gibt es mehrere Strategien, um mit höheren Chipkosten umzugehen: Sie können Preiserhöhungen an Endkunden weitergeben, die Margen reduzieren, Komponenten‑Kombinationen ändern (z. B. weniger RAM/Storage in bestimmten Varianten), ältere Prozessknoten für Massenmodelle weiterverwenden oder stärkere vertikale Integration (eigene AP‑Designs) anstreben. Apple ist ein Beispiel für vertikale Integration, während andere Hersteller weiterhin auf Qualcomm, MediaTek oder Samsung Foundry als AP‑Zulieferer angewiesen sind. Jede Strategie hat Vor‑ und Nachteile in Bezug auf Time‑to‑Market, Investitionsbedarf und Abhängigkeit von Zulieferern.

Marktanalysten beobachten zudem die Preiselastizität der Nachfrage für Premium‑Smartphones. In bestimmten Segmenten kann ein moderater Preisanstieg toleriert werden, wenn technische Innovationen (bessere Kamera, längere Akkulaufzeit, KI‑Funktionen) den Mehrwert rechtfertigen. Gleichzeitig riskieren OEMs bei zu hohen Preisaufschlägen, Kunden in Richtung preiswerterer Wettbewerber oder älterer Modelljahre zu verlieren. Deshalb werden viele Hersteller differenzierte Preisstrategien testen, etwa höhere Preise für Ultra‑Modelle mit 2‑nm‑APs und stabilere Preise für Basismodelle mit 3‑nm‑ oder 4‑nm‑Chips.

Schließlich beeinflussen geopolitische Faktoren und Investitionsentscheidungen die Chipkosten und Kapazitätsallokationen. Staatliche Förderprogramme, Exportkontrollen und nationalstrategische Investitionen in Halbleiterfertigung können die globale Kapazitätslandschaft verändern. Für Verbraucher bedeutet das: Preisbewegungen bei High‑End‑Smartphones sind das Ergebnis einer komplexen Wechselwirkung technischer Innovationen, Fertigungskosten, Kapazitätsverfügbarkeit und strategischer Geschäftsentscheidungen entlang der Lieferkette.

Zusammenfassend lässt sich sagen, dass die beobachtete Erhöhung der Waferpreise bei TSMC für den N3P‑Prozess eine plausible Erklärung dafür bietet, warum einige Galaxy S26‑Modelle mit höheren Preisen auf den Markt kommen könnten. Langfristig werden die Einführung des 2‑nm‑Nodes, die Verfügbarkeit und Allokation von Fertigungskapazitäten sowie die Entscheidung von OEMs über Preisstrategie und Integration darüber entscheiden, wie stark diese Kostentrends beim Endkunden ankommen.

Quelle: phonearena

Kommentar hinterlassen